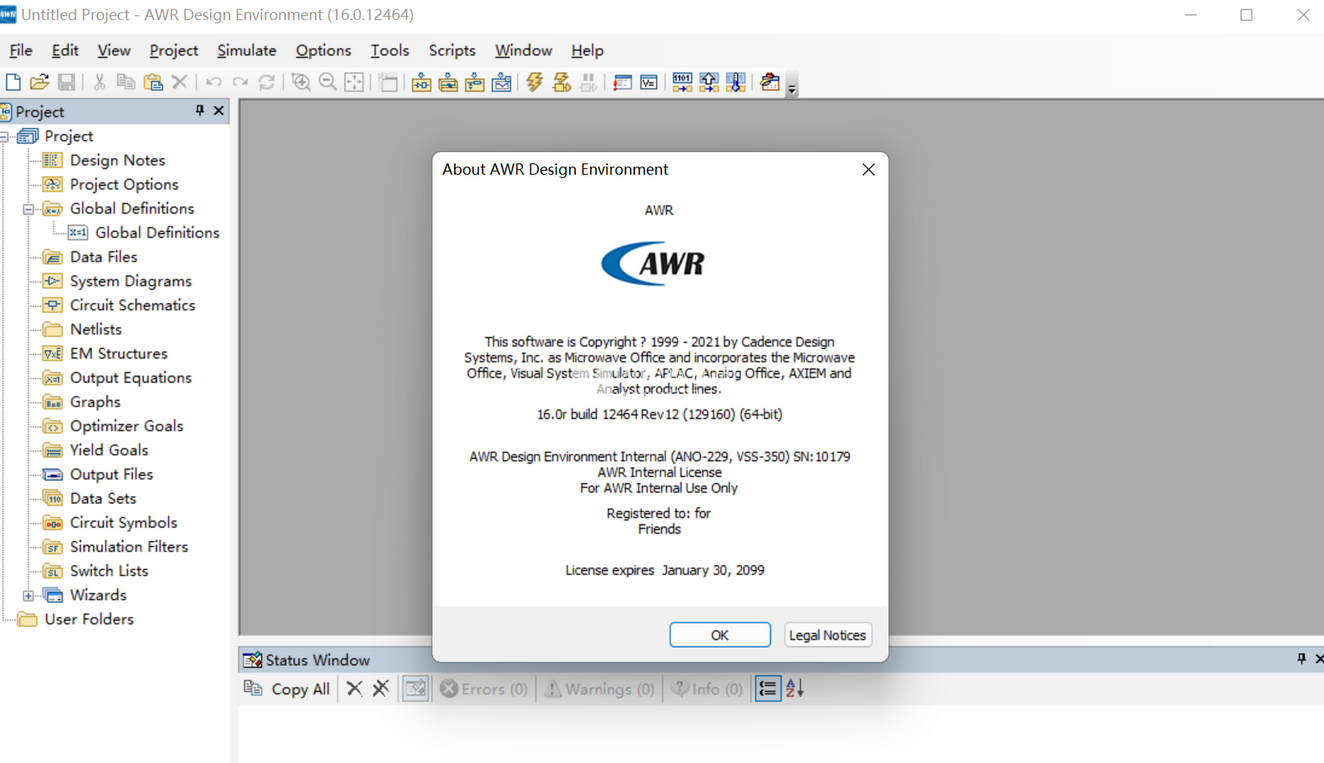

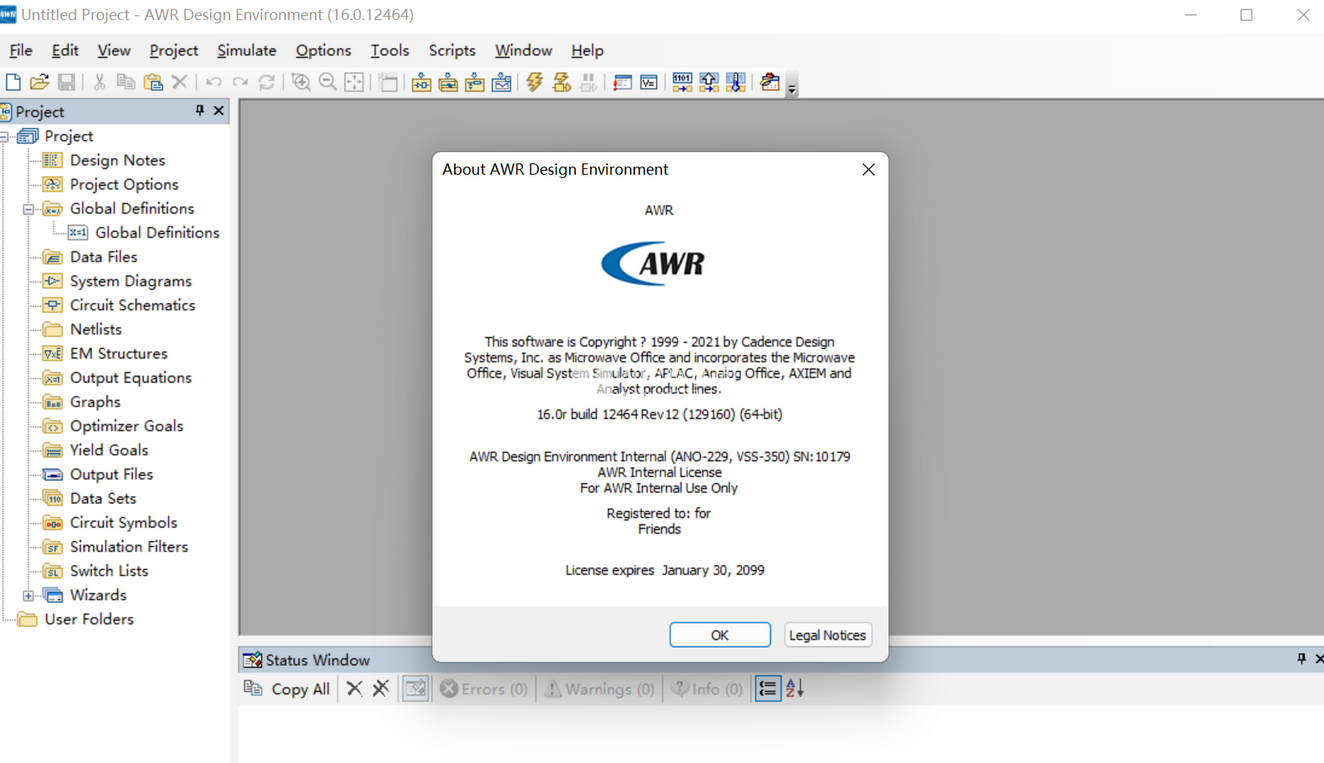

AWR Design Environment with Analyst16ЦЦНтАцЪЧЕчзгЩшМЦздЖЏЛЏЃЈEDAЃЉШэМўЃЌЪЙгУПЩЮЊгУЛЇЬсЙЉвЛСїЕФЗТецММЪѕКЭЩшМЦздЖЏЛЏЃЌЬсЙЉгыгУгкПЊЗЂЛьКЯаХКХЕчзгЯЕЭГЕФИќЙуЗКЕФEDAЙЄОпРрБ№ЕФЛЅВйзїадЃЌCadence AWR Design EnvironmentЦНЬЈЕФзюаТАцБОЃЌАцБО16(V16)ЃЌАќРЈMicrowave OfficeШэМўЁЃVisual System Simulator(VSS)ЭЈаХКЭРзДяЯЕЭГЩшМЦШэМўЃЌвдМАAXIEM 3DЦНУцЕчДХ(EM)КЭAnalyst 3D FEMФЃФтЦїЃЌв§ШыСЫЭЛЦЦадЕФПчЦНЬЈЛЅВйзїадЃЌвджЇГжПчCadence Virtuoso®ЕФвьЙЙММЪѕПЊЗЂЕФRF IPМЏГЩЃЌAllegro PCBЁЂSpectreЗТецКЭICЗтзАЩшМЦЦНЬЈЃЌгыОКељЙЄзїСїГЬЯрБШЃЌжмзЊЪБМфзюЖрПЩМѕЩй50%ЁЃV16АцБОНјвЛВНв§ШыСЫгыClarity 3D SolverКЭCelsius Thermal SolverЕФЮоЗьМЏГЩЃЌЮЊДѓЙцФЃИДдгЩфЦЕЯЕЭГЕФЕчШШадФмЗжЮіЬсЙЉСЫВЛЪмЯожЦЕФФмСІЁЃНшжњAWR Design Environment V16ЃЌCadenceЭЈЙ§ЙЋЫОЕФIntelligent System DesignеНТдНтОіЩфЦЕ/ЮЂВЈЩшМЦКЭМЏГЩЮЪЬтЃЌИУеНТдЮЊЕчзгЯЕЭГЕФЫљгаЩшМЦдЊЫиЬсЙЉМЦЫуШэМўЙІФмЁЃИУеНТдЕФКЫаФЪЧзПдНЕФЩшМЦЃЌАќРЈгХЛЏЕФEDAЙЄОпзщКЯЃЌОпгавЛСїЕФЩфЦЕЁЂЮЂВЈКЭКСУзВЈЕчТЗЁЂЯЕЭГКЭЕчДХЗжЮіЁЂгУгкАыЕМЬхЁЂЗтзАКЭPCBЩшМЦЕФIPвдМАПЩРЉеЙЗУЮЪдкдЦжаЁЃ

AWR Design Environment16аТЙІФм

1ЁЂЧПДѓЕФ

НЋИХФюзЊЛЏЮЊеце§ЕФЩфЦЕ/ЮЂВЈзщМўЃЌеыЖдадФмНјаагХЛЏЃЌВЂзМБИКУЧсЫЩМЏГЩЕНЕквЛДЮе§ШЗЕФЖрНсЙЙЯЕЭГжа

2ЁЂгаМћЕи

ЭЈЙ§НєУмёюКЯЕФЕчДХ (EM) КЭШШЗжЮіВЖЛёеце§ЕФ RF ЯЕЭГадФмЃЌвдНтОіДѓаЭИДдгНсЙЙКЭЗЂШШ RF ЙІТЪгІгУ

3ЁЂСЌНгЕФ

ПЩЧЖШыЧвПЩжиИДЪЙгУЕФ Cadence Microwave Office® ЕчТЗЩшМЦШэМў IP ПЊДДСЫЧАЫљЮДгаЕФПчЦНЬЈЙЄзїСїГЬаТЪБДњЃЌЪЪгУгкаОЦЌЁЂЗтзАЁЂЕчТЗАхКЭФЃПщЩшМЦЕФ Allegro КЭ Virtuoso ЦНЬЈ

4ЁЂВЂаадЖГЬЗТец

зївЕЕїЖШГЬађЯждкжЇГжЖрИіЭЌЪБНјааЕФдЖГЬЖгСаЃЌЪЙЩшМЦШЫдБФмЙЛдкБОЕиЛђдЖГЬВЂаадЫааГЄЕчТЗЗТецЛђгХЛЏзївЕЁЃEM НсЙЙЯждкжЇГжАДЮФЕЕдЖГЬЖгСабЁдёЃЌВЂЧв Cadence AXIEM® ЦНУц EM КЭ Analyst™ 3D гаЯодЊЗНЗЈ (FEM) ФЃФтЖМПЩвддкдЖГЬ Linux МЏШКЩЯдЫааЁЃ

5ЁЂЖЏЬЌПеЖДКЭздЖЏЭјТчСЌНгЬсШЁ

Microwave Office ШэМўжааТЕФЖЏЬЌПеЖДВМОжФЃЪНЛсздЖЏЮЊИїжжЛцЭМВуЬэМгВМОжаЮзДКЭЭјТчжЎМфЕФМфЯЖЃЌВЂгЩВМОжЙ§ГЬЮФМў (LPF) жажИЖЈЕФдМЪјЙцдђЖЈвхЁЃР§ШчЃЌПЩвдЮЊЭЈЙ§НгЕиЛђаХКХЦНУцВМЯпЕФаХКХзпЯпздЖЏЬэМгМфЯЖЁЃЖюЭтЕФЭјТчЙмРэЙІФмгажњгкЪЖБ№ВМОжКЭдРэЭМжаЕФЭјТчЖдЯѓЃЌаТЕФСЌНгФЃЪНПЩЪЕЯжаЮзДгыжиЕўЭјТчЕФздЖЏЙиСЊЁЃ

6ЁЂАцБОПижЦ

АцБОПижЦЙмРэзщЩшМЦЯюФПЃЌдЪаэЖдВЩгУЖржжВЛЭЌММЪѕЕФИДдгЖрЙІФмЩшМЦНјаазщЩшМЦЪ§ОнЙмРэЁЃЕБЖрИігУЛЇдкАцБОПижЦЪ§ОнПтЛђжабыДцДЂПтжаБрМЭЌвЛЮФМўЪБЃЌЫќЛЙПЩвдЗРжЙЮовтЕФЮФМўИВИЧЁЃ

7ЁЂВМОжзпЯпЛЅСЌНЈФЃ

Cadence Visual System Simulator™ (VSS) ЭЈаХКЭРзДяЯЕЭГЩшМЦШэМўжаЕФаТЛЅСЌ (INTERCONN) ЯЕЭГФЃПщЖдДЋЪфЯпЫ№КФЁЂзшПЙЪЇХфКЭёюКЯЕФгАЯьНјааНЈФЃЁЃИУФЃПщОпгаЮхжжВЛЭЌЕФВйзїФЃЪНЃЌвдДйНјЩшМЦСїГЬЃЌДгВМОжЕФДжТдЙРМЦПЊЪМЃЌЕНдк EM ЗТецжаЪЙгУзюже PCB ВМОжзпЯпЁЃ

8ЁЂЕЅДПаЮгХЛЏЦї

ОпгаПЩБфВНГЄЕФ Microwave Office ШэМўжадіЧПЕФЕЅЯпГЬКЭВЂааЕЅДПаЮгХЛЏЦїБШвдЧАЕФЕЅДПаЮгХЛЏЦїЬсЙЉСЫИќДѓЕФСщЛюадЃЌЪЙЫќУЧИќЙуЗКЕиЪЪгУКЭ/ЛђЕжПЙОжВПзюаЁжЕЁЃ

9ЁЂЩфЦЕЗХДѓЦїЙІТЪБЅКЭЖШКЭБЖЦЕЦїНЈФЃ

Жд VSS ШэМўдкБЅКЭзДЬЌЯТЖд RF ЗХДѓЦїНЈФЃЕФИФНјЯждкПЩвдЩњГЩИќЦНЛЌЕФЙІТЪЪфГігыЙІТЪЪфШыЧњЯпЁЃетаЉИФНјЪЪгУгкЪБгђЁЂRF дЄЫуЗжЮіКЭ RF Inspector (RFI) ФЃФтЁЃДЫЭтЃЌVSS ШэМўЕФааЮЊБЖЦЕЦїФЃаЭвбеыЖдБЅКЭЪфГіЙІТЪКЭдгЩЂЕчЦННјааСЫИФНјЃЌдкЪБгђЁЂRF дЄЫуЗжЮіКЭ RFI ЗТецжЎМфВњЩњСЫУмЧаЕФвЛжТадЁЃдЄВтадФмЖдЪфШыЙІТЪБфЛЏВЛЬЋУєИаЃЌгыЮяРэБЖЦЕЦїЩшБИЕФааЮЊЯрЦЅХфЁЃ

АВзАМЄЛюНЬГЬ

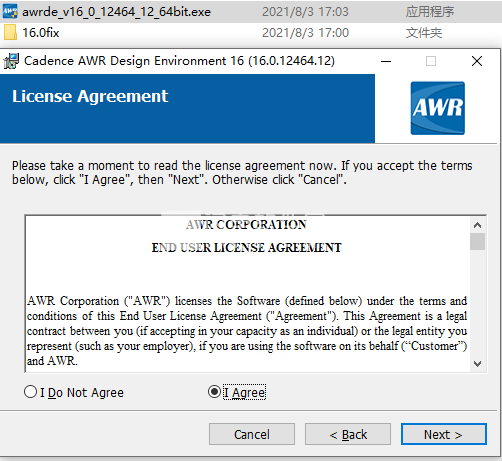

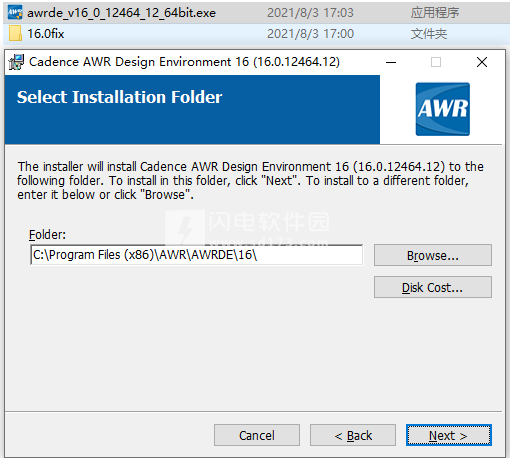

4ЁЂАВзАЭъГЩЃЌЭЫГіЯђЕМЃЌНЋ16.0fixЮФМўМажаЕФВЙЖЁЮФМўИДжЦЕНАВзАФПТМжаЃЌЕуЛїЬцЛЛФПБъжаЕФЮФМў

AWR Design Environment with Analyst 16(V16)ОпгаЭЛЦЦадЕФПчЦНЬЈЛЅВйзїадЃЌжЇГжЩфЦЕЕНКСУзВЈ(mmWave)жЊЪЖВњШЈ(RF IP)МЏГЩЃЌгУгкПчаавЕСьЯШЕФCadence VirtuosoЩшМЦЦНЬЈвдМАAllegro PCBКЭICЗтзАЩшМЦЦНЬЈЁЃV16АцБОЛЙв§ШыСЫгыClarity 3DЧѓНтЦїКЭЩуЪЯЖШШШЧѓНтЦїЕФЮоЗьМЏГЩЃЌЮЊДѓЙцФЃИДдгЩфЦЕЯЕЭГЕФЕчШШадФмЗжЮіЬсЙЉВЛЪмЯожЦЕФФмСІЁЃаТЕФAWRЩшМЦЛЗОГЃЌАќРЈMicrowave OfficeЕчТЗЩшМЦШэМўЃЌЪЙПЭЛЇФмЙЛИпаЇЕиЩшМЦгУгкЦћГЕЁЂРзДяЯЕЭГКЭАыЕМЬхММЪѕЕФ5GЮоЯпКЭСЌНгЯЕЭГЃЌВЂИќПьЕиНјШыЪаГЁЁЃгыОКељЙЄзїСїГЬЯрБШЃЌV16АцБОжаЕФЦНЬЈКЭЧѓНтЦїМЏГЩПЩНЋжмзЊЪБМф(TAT)МѕЩйЖрДя50%ЁЃ

AWR Design Environment with Analyst 16.02R МЄЛюАц

AWR Design Environment with Analyst 16.02R МЄЛюАц

AWR Design Environment with Analyst 16.02R МЄЛюАц

AWR Design Environment with Analyst 16.02R МЄЛюАц