ЁЁЁЁЁЁЁЁЁЁЁЁЁЁЁЁ

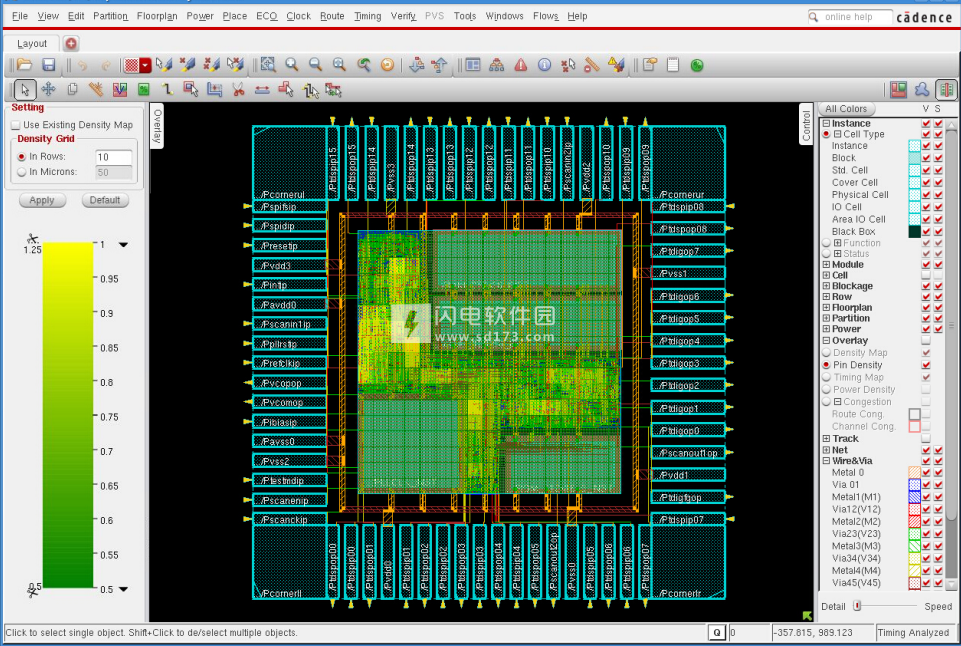

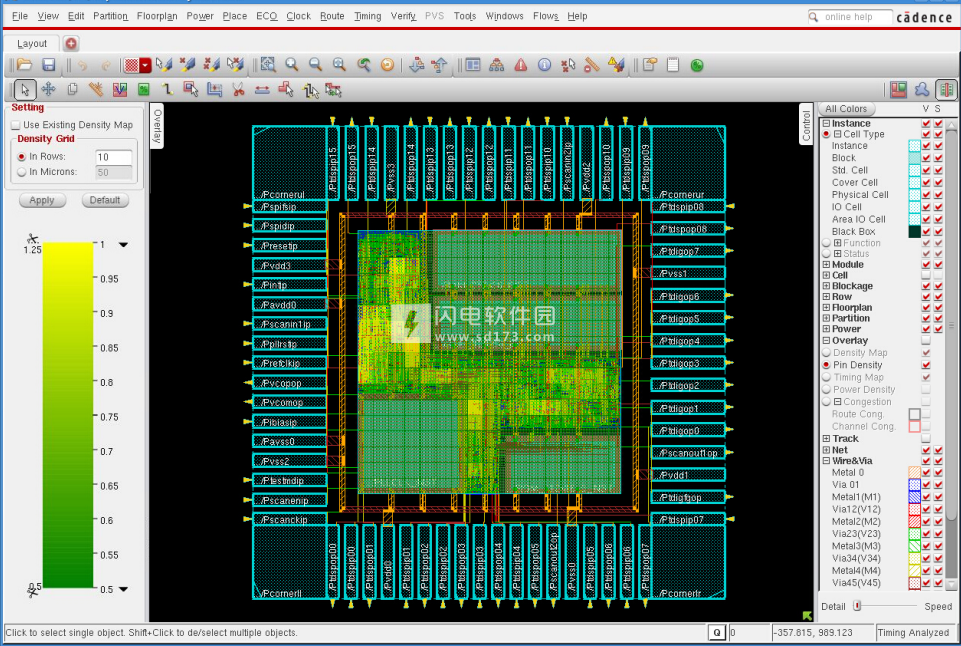

Cadence INNOVUSЦЦНтАцЪЧаТвЛДњЕФЮяРэЩшМЦЪЕЯжНтОіЗНАИЃЌЪЕЯжЯЕЭГОпБИЕФМИЯюКЫаФММЪѕПЩвдАяжњЮяРэЩшМЦЙЄГЬЪІдкТњзуЙІКФ/УцЛ§дЄЫувЊЧѓЯТЪЕЯжзюМбЕФадФмЁЂЛђепдкТњзуЦЕТЪжИБъЕФЭЌЪБШЗБЃЙІКФ/УцЛ§зю

Cadence INNOVUSЦЦНтАцЪЧаТвЛДњЕФЮяРэЩшМЦЪЕЯжНтОіЗНАИЃЌЪЕЯжЯЕЭГОпБИЕФМИЯюКЫаФММЪѕПЩвдАяжњЮяРэЩшМЦЙЄГЬЪІдкТњзуЙІКФ/УцЛ§дЄЫувЊЧѓЯТЪЕЯжзюМбЕФадФмЁЂЛђепдкТњзуЦЕТЪжИБъЕФЭЌЪБШЗБЃЙІКФ/УцЛ§зюаЁЁЃгУгкдкЖрКЫЙЄзїеОЩЯДІРэДѓаЭЩшМЦКЭжЇГжЖрЯпГЬвдМАЭЈЙ§МЦЫуЛњЭјТчНјааЗжВМЪНДІРэЕФДѓЙцФЃВЂааМмЙЙЁЃаТЕФЛљгк GigaPlace™ ЧѓНтЦїЕФВМОжММЪѕЃЌЫќЪЧЫЩГкЧ§ЖЏКЭЭиЦЫЁЂв§НХЗУЮЪЁЂКЭбеЩЋИажЊЃЌвдЬсЙЉзюМбЕФСїЫЎЯпВМОжЁЂЯпГЄЁЂРћгУТЪКЭ PPAЁЃИпМЖЁЂЖрЯпГЬЁЂВуИажЊгХЛЏв§ЧцЃЌгЩЪБађКЭЙІТЪЧ§ЖЏвдНЕЕЭЖЏЬЌКЭаЙТЉЙІТЪЁЃ ЖРЬиЕФВЂЗЂЪБжгКЭЪ§ОнТЗОЖгХЛЏв§ЧцЃЌвдНЕЕЭЙІКФЛёЕУИќКУЕФПчНЧПЩБфадКЭадФмЁЃ ОпгаИњзйИажЊЪБађгХЛЏЕФЯТвЛДњЫЩГкЧ§ЖЏВМЯпЃЌПЩдкдчЦкНтОіаХКХЭъећадВЂИФЩЦВМЯпКѓЯрЙиадЁЃШЋСїГЬЖрФПБъММЪѕвджЇГжВЂЗЂЕчЦјКЭЮяРэгХЛЏЁЃ ЭЈЙ§ЭЈгУ UI КЭгУЛЇУќСюЪЕЯжПЩЖЈжЦЕФСїГЬЃЌКИЧзлКЯЁЂЪЕЪЉКЭЧЉКЫЃЌВЂЬсЙЉПЩППЕФБЈИцКЭПЩЪгЛЏЃЌгажњгкЬсИпЩшМЦаЇТЪКЭЩњВњСІ

ЙІФмЬиЩЋ

1ЁЂаТЕФЫЩГкЧ§ЖЏЕФЗХжУММЪѕ

Innovus ЪЕЪЉЯЕЭГВЩгУаТЕФ GigaPlace в§ЧцЃЌЫќИФБфСЫЗХжУЕФЗНЪНВЂдіЧПСЫ PPAЁЃВМОжДЋЭГЩЯЪЧ“ЪБађИажЊ”КЭ“ЧсЮЂ”гыЪЕЯжЯЕЭГжаЕФЦфЫћв§ЧцМЏГЩЃЌР§ШчЪБађЗжЮіКЭгХЛЏЁЃСэвЛЗНУцЃЌGigaPlace в§ЧцЪЧЫЩГкЧ§ЖЏКЭНєУмМЏГЩЕФЁЃЭЈЙ§етжжЗНЗЈЃЌв§ЧцЭЈЙ§НЈСЂТЗОЖЕФЫЩГкТжРЊВЂИљОнетаЉЪБађЫЩГкжДааВМОжЕїећЃЌАяжњНЋЕЅдЊЗХжУдкЪБађЧ§ЖЏФЃЪНЯТ GigaPlace в§ЧцЖдОЋШЗЕФЕчЦјдМЪјКЭЮяРэдМЪјНјааНЈФЃЃЌР§ШчВМОжЙцЛЎЁЂТЗгЩЭиЦЫ- ЛљгкЕчЯпГЄЖШКЭгЕШћЁЃЫќЛЙМЏГЩСЫ Cadence ЕФЪБађКЭЙІТЪЧ§ЖЏгХЛЏв§ЧцЕФЪ§бЇФЃаЭЃЌетЪЧ Innovus ЪЕЪЉЯЕЭГЕФСэвЛИізщГЩВПЗжЁЃетжжМЏГЩЪЙЕчЦјКЭЮяРэжИБъЕФВЂЗЂЁЂЪеСВгХЛЏГЩЮЊПЩФмЁЃФњЛЙПЩвдДгЕчЦјдМЪјжаздЖЏЬсШЁЩшМЦвтЭМЃЌДгЖјИќКУЕигХЛЏЮяРэжИБъЁЃ

Innovus ЪЕЯжЯЕЭГОпгаШЋОжгХЛЏВпТдКЭаТгБЕФЪ§жЕЧѓНтЦїЃЌПЩБмУтОжВПзюаЁжЕЕФЯнкхЁЃетБмУтСЫСїГЬВЛЭЌВНжшжЎМфДњМлИпАКЕФЩшМЦЕќДњЃЌВЂвдзюМб PPA ЪЕЯжИќПьЕФЩшМЦЪеСВЁЃ

Г§СЫНтОіжиЕўКЭЯпТЗГЄЖШжЎЭтЃЌGigaPlace в§ЧцЛЙНтОіСЫгЩУХбгГйЁЂДэЮѓ/ЖржмЦкТЗОЖЁЂВуЗжХфКЭгЕШћЪБађаЇгІЧ§ЖЏЕФЫЩГкЮЪЬтЁЃвђДЫЃЌФњПЩвдЛёЕУИќКУЕФзмИКЪБВю (TNS)/зюВюИКЪБВю (WNS)ЁЂЯпГЄЁЂгЕШћЁЂРЉеЙКЭЙІТЪЁЃзлЩЯЫљЪіЃЌGigaPlace в§ЧцЪЧЃК

• ЕчЧ§ЖЏЃЌНтОіЖрФЃ/ЖрНЧ (MMMC) ЫЩГкЁЂЦЋаБКЭЙІТЪ

• ЮяРэЧ§ЖЏЃЌПМТЧТЗгЩЭиЦЫЁЂВуЁЂбеЩЋКЭв§НХЗУЮЪ

• гХЛЏЧ§ЖЏЃЌПМТЧУХЕФДѓаЁКЭЛКГх

в§НХЗУЮЪвбГЩЮЊаТЕФЩшМЦБеКЯжИБъЁЃ GigaPlace в§ЧцЃЌШчЭМ 1 ЫљЪОЃЌПМТЧв§НХУмЖШЃЌЬсЙЉздЪЪгІв§НХЗУЮЪСїЃЌИљОнЯрСкЪЕР§ЕФв§НХЗУЮЪЯожЦздЖЏЗжИєЕЅдЊИёЃЌЖјВЛНіНіЪЧИпОжВПв§НХУмЖШЁЃИУЙЄОпжаЕФзЈгаЫуЗЈШЋОжЙцЛЎСЫТЗгЩЦїНЋШчКЮЗУЮЪУПИів§НХЃЈетЪЧЛљгкЪЕР§ЃЌЖјВЛЪЧПтЕЅдЊЃЉЁЃ GigaPlace в§ЧцОпгаПМТЧИќЖрЩшМЦЙцдђМьВщ (DRC) ЙцдђКЭдЄВМЯпЕФЕЅдЊРЉеЙГЩБОКЏЪ§ЁЃгХЛЏГЩБОКЏЪ§ЭЌЪБПМТЧЫЎЦНКЭДЙжБЕЅдЊИёРЉеЙЃЌВЂЧвдкКЯЗЈЛЏЙ§ГЬжаДцдкааФкПеМфдгЫЃЙІФмЁЃ

GigaPlace в§ЧцВЩгУздЖЏУмЖШЦСФЛММЪѕЃЌЭЈЙ§дкЦНУцЭМв§Ц№ЕФИпСїСПЧјгђздЖЏЬэМгУмЖШЦСФЛЃЌМђЛЏСЫНтОігЕЖТЕФЙ§ГЬЁЃИУЫуЗЈЗжЮіЦНУцЭМЁЂСїСПФЃЪНКЭгЕШћЭМЃЌвдЪЙБъзМаЁЧјдЖРыгЕШћЧјгђЃЌР§ШчеЭЈЕРЁЂВлПкКЭКъБпНчЁЃетгажњгкМѕЩйгЕЖТЃЌЖјЮоашФњздМКЬэМгетаЉУмЖШЦСФЛ

2ЁЂИпМЖЪБађКЭЙІТЪЧ§ЖЏгХЛЏ

ЭЈЙ§ЦфТЗгЩИажЊгХЛЏЙІФмЃЌInnovus ЪЕЪЉЯЕЭГжаЕФЯТвЛДњЖрЯпГЬИпМЖЪБађКЭЙІТЪЧ§ЖЏгХЛЏв§ЧцПЩвдЃК

• ЪЖБ№ГЄЪБМфЙиМќЭјТч

• ВщбЏаТЕФгЕШћИњзйЛљДЁЩшЪЉЃЌвдШЗБЃЩЯВугаПЩгУПеМф

• дкЩЯВужиаТЛКГхетаЉЭјТч

ЮЊСЫИФЩЦЪБЛњ

НшжњетаЉЙІФмЃЌФњПЩвддкећИіВМЯпЧАгХЛЏСїГЬжаЮЌЛЄЙиМќВуЗжХфЁЃетаЉЗжХфБЛДЋЕнЕНЯЕЭГЕФЯТвЛДњДѓЙцФЃВЂааШЋОжВМЯпв§ЧцЃЌвдБузюжеВМЯпвВНЋОпгае§ШЗЕФВуЗжХфЁЃ

гХЛЏв§ЧцЛЙгажњгкНЕЕЭЖЏЬЌКЭаЙТЉЙІТЪЃЌЭЌЪБДйНјзюМбадФмЁЃЯЕЭГФкВПЕФОіВпв§ЧцРћгУЗсИЛЕФЙІТЪИажЊзЊЛЛПтРДж№ВНжДааПЩгУбЁЯюВЂдкВЛгАЯьЪБађЕФЧщПіЯТЛиЪеЙІТЪЁЃ

етзюДѓЯоЖШЕиМѕЩйСЫаЙТЉЃЌвдМАШЋОжФкВПКЭПЊЙиЙІТЪЁЃ

ИУв§ЧцжЇГжЖржжИёЪНЃКVCDЁЂTCFЁЂSAF КЭ SAIFЁЃШчЙћЧаЛЛЛюЖЏЪ§ОнВЛПЩгУЃЌдђв§ЧцВЩгУЛљгкИХТЪЕФДЋВЅЁЃ

вђДЫЃЌв§ЧцдкбАевзюМбЙІТЪНтОіЗНАИвдНЕЕЭ SoC ЕФЙІТЪЖјВЛгАЯьадФмЛђУцЛ§ЗНУцзіГізюМбХаЖЯЁЃ

3ЁЂЪЙгУеце§ЕФЖрЯпГЬНјааЪБжгВЂЗЂгХЛЏ

Innovus ЪЕЯжЯЕЭГОпгаЯТвЛДњЪБжгВЂЗЂгХЛЏв§ЧцЃЌОпгаеце§ЕФЖрЯпГЬЁЂдіЧПЕФгагУЦЋаБКЭСїМЏГЩЁЃИУв§ЧцНЋЮяРэгХЛЏгыЪБжгЪїзлКЯ (CTS) ЯрНсКЯЃЌЭЌЪБжБНгЛљгкДЋВЅЕФЪБжгФЃаЭЙЙНЈЪБжгВЂгХЛЏТпМбгГйЁЃЫљгагХЛЏОіВпЖМЛљгкецЪЕЕФДЋВЅЪБжгЃЌВЂПМТЧСЫЪБжгУХЁЂЪБжгМфТЗОЖКЭЦЌЩЯБфЛЏ (OCV) НЕЖюЁЃ

ЪЕЯжЯЕЭГжаЕФаТ FlexH ЙІФмЬсЙЉСЫвЛжжЭиЦЫНсЙЙЃЌИУНсЙЙдкЭиЦЫЩЯОЁПЩФмНгНќ H ЪїЃЌВЂдкВЛЭЌЕФШэдМЪјКЭгВдМЪјжЎМфНјааШЈКтЁЃДЫЙІФмНЋ H ЪїЗНЗЈУёжїЛЏЕНЯжЪЕЪРНчЕФ SoC ЩшМЦЛЗОГжаЁЃ

ШчЙћУЛгаДЫЙІФмЃЌЩшМЦШЫдБЭЈГЃЛсЪЙгУЭјИёЛђЪжЙЄДДНЈЕФЪї——МмЙЙЪмЯоЧвКФЕчЕФЗНЗЈЁЃ FlexH ЙІФмВЩгУЯШНјЕФЦєЗЂЪНЫбЫїЫуЗЈЃЌИУЫуЗЈЬНЫїЪ§АйЭђжжВЛЭЌЕФПЩФмЪїНсЙЙЃЌвдевЕНБмУтзшШћКЭЕчдДЙьжЎМфЕФзюМбелждЗНАИЁЃИУЫуЗЈзёЪиЗжЧјЁЂФЃПщКЭЙІТЪгђдМЪјЃЌВЂгХЛЏВхШыбгГйЁЂЙІТЪКЭЦЋаБ

4ЁЂТЗгЩКЭЛЅСЌгХЛЏв§Чц

Innovus ЪЕЪЉЯЕЭГОпгаОЙ§бщжЄЕФВМЯпКЭЛЅСЌгХЛЏв§ЧцЃЌПЩДйНјдкЪБађЁЂУцЛ§ЁЂЙІТЪЁЂаХКХЭъећадКЭжЦдьФПБъЗНУцЕФзмЬхВМЯпЪеСВЁЃ ИУв§ЧцВЩгУДѓЙцФЃВЂааМмЙЙЃЌЬсЙЉШЋСїГЬЪБађЙиСЊЁЂШЗЖЈадЖрЯпГЬКЭСщЛюЕФ 2D/3D гЕШћФЃЪНЁЃ

дчЦкШЋОжТЗОЖ (eGR) ЙІФмНјвЛВНИФНјСЫ TNS КЭ WNSЃЌвдМАПЩдЄВтЕФЩшМЦЪеСВЁЃ ТЗгЩКЭЛЅСЌгХЛЏв§ЧцЛЙЃК

• дкЯъЯИТЗгЩжЎЧАаоИДаХКХЭъећадЮЪЬт

• МѕЩйВМЯпЧАКЭВМЯпКѓжЎМфЕФЪБађЬјдО

• дЪаэИќИФЭјБэКЭЕЅдЊЮЛжУ

NanoRoute™ ЙЄОпЛЙЬсЙЉНсЙЙЛЏВМЯпЙІФмЃЌПЩгУгкбЁдёаддЄВМЯпЁЂЦСБЮКЭИпЦЕзмЯпВМЯпЃЌвдМАОпгаГЄЖШ/ЕчзшЦЅХфвЊЧѓЕФЭјТчЁЃ

5ЁЂМгЫйTAT

Innovus ЪЕЪЉЯЕЭГЭЈЙ§ИїжжЙІФмМгЫйЪ§зжЩшМЦ TATЃЌАќРЈЦфШЋСїГЬДѓЙцФЃВЂааМмЙЙЁЃИУМмЙЙжЇГждкЖрИі CPU ЩЯЭЌЪБжДааЖрЯпГЬШЮЮёЃЌЦфЩшМЦЪЙЕУЯЕЭГПЩвдЪЙгУБъзМгВМўЃЈЭЈГЃУПКа 8-16 Иі CPUЃЉЩњГЩвЛСїЕФ TATЁЃДЫЭтЃЌЖдгкОпгаИќЖрЪЕР§Ъ§ЕФЩшМЦЃЌСїПЩвддкИќЖр CPU ЩЯНјааРЉеЙЁЃЯЕЭГЯШНјЕФЪБађКЭЙІТЪЧ§ЖЏгХЛЏв§ЧцЬсЙЉЯпГЬЛЏ MMMC ЪБађЁЃЫцзХ MMMC ЪгЭМЪ§СПЕФдіМгЃЌв§ЧцЬсЙЉСЫбЧЯпадМгЫйЁЃ

ЯЕЭГЕФВМЯпв§ЧцЩшМЦЮЊдкЖюЭтЕФ CPU ЩЯДІРэВМЯпКЭВМЯпКѓБеКЯ——ШчЙћашвЊИќДѓЕФЩшМЦЃЌдђГЌЙ§ 100 ИіЁЃ

дкЦфДІРэЫйЖШЕФжЇГжЯТЃЌТЗгЩв§ЧцЛсИљОнЖдЪБађЁЂУцЛ§ЁЂЙІКФЁЂПЩжЦдьадКЭСМТЪЕФгАЯьЭЌЪБЦРЙРКЭгХЛЏЛЅСЌЭиЦЫЁЃЦОНшЦфАДЙЙдьаЃе§ЕФЗНЗЈЃЌИУв§ЧцПЩвдМДЪБНтОіЧБдкЕФЫЋЭМАИГхЭЛЃЌвдДДНЈЕквЛДЮЖдЫЋЭМАИКЭ DRC е§ШЗЧвУцЛ§аЇТЪИќИпЕФВМЯпЭиЦЫЁЃв§ЧцХфБИШЗЖЈадЖрЯпГЬБГАхЃЌЬсЙЉШЋСїЪБађЙиСЊЃЌВЂЬсЙЉСщЛюЕФ2D/3DгЕШћФЃЪНЁЃЫќЛЙОпгаЛљгкЙьЕРЕФгХЛЏЫуЗЈЃЌПЩдкЯъЯИВМЯпжЎЧАаоИДаХКХЭъећадЮЪЬтЃЌМѕЩйВМЯпЧАКЭВМЯпКѓжЎМфЕФЪБађЬјдОЃЌВЂЪЕЯжИќПьЕФЩшМЦЪеСВЁЃ

6ЁЂИпМЖНкЕуЪЕЯжЙІФм

Innovus ЪЕЪЉЯЕЭГОпгаЭъећЕФЙІФмМЏЃЌПЩТњзудкИпМЖ FinFET НкЕуЩЯЪЕЪЉЫљашЕФвЊЧѓЁЃЬиЪтЙІФмПЩгУгкдкВМОжЙцЛЎНзЖЮЕФдчЦкДІРэКъКЭБъзМЕЅдЊЕФВМОжашЧѓЁЃВМОжв§ЧцвбИќаТвдДІРэИпМЖНкЕуПтЕФв§НХЗУЮЪвЊЧѓЃЌNanoRoute ЙЄОпПЩвдДІРэКЭгХЛЏздЖдзМЫЋЭМАИЛЏММЪѕЕФВМЯпЁЃаТЕФ Via Pillar ВхШыСїГЬКЭЗНЗЈЪЙФњФмЙЛдкТњзуЕчЧЈвЦвЊЧѓЕФЭЌЪБЬсИпадФмЁЃ

ИќаТЕФгХЛЏв§ЧцПЩвдзМШЗЕиФЃФтЕЭЕчбЙаЇгІЃЌвдЬсЙЉНгНќЧЉКЫжЪСПЕФОВЬЌЪБађНсЙћЃЌДгЖјМгПьЩшМЦЪеСВЫйЖШЁЃ

7ЁЂвзгкЪЙгУЕФЭЈгУгУЛЇНчУц

Innovus ЪЕЯжЯЕЭГгы Cadence ЕФ Tempus™ ОВЬЌЪБађЗжЮіЁЂQuantus™ ЬсШЁКЭ Voltus™ ЕчдДЭъећадММЪѕМЏГЩЃЌвђДЫФњПЩвддкЮяРэЪЕЯжЕФдчЦкНзЖЮзМШЗЕиЖдЪБађЁЂМФЩњаЇгІвдМАаХКХКЭЕчдДЭъећадЮЪЬтНјааНЈФЃЁЃетгажњгкИќПьЕиЪеСВетаЉЕчЦјжИБъЃЌДгЖјМгПьЩшМЦЪеСВЁЃ

ИУЪЕЪЉЯЕЭГОпгагы Cadence ЕФ Genus™ злКЯНтОіЗНАИКЭ Tempus ЪБађЧЉКЫНтОіЗНАИЕФЭЈгУ UIЁЃИУЯЕЭГМђЛЏСЫУќСюУќУћЃЌВЂдкетаЉ Cadence Ъ§зжКЭЧЉКЫЙЄОпжЎМфЕїећСЫЭЈгУЪЕЪЉЗНЗЈЁЃР§ШчЃЌЩшМЦГѕЪМЛЏЁЂЪ§ОнПтЗУЮЪЁЂУќСювЛжТадКЭЖШСПЪеМЏЕФЙ§ГЬЖМЕУЕНСЫОЋМђКЭМђЛЏЁЃДЫЭтЃЌЛЙЬэМгСЫИќаТКЭЙВЯэЕФЗНЗЈРДдЫааЁЂЖЈвхКЭВПЪ№ВЮПМСїЁЃетаЉИќаТЕФНчУцКЭВЮПМСїЭЈЙ§дкКЫаФЪЕЯжКЭЧЉКЫВњЦЗжЎМфЬсЙЉЪьЯЄЕФНчУцРДЬсИпЩњВњСІЁЃФњПЩвдРћгУЪМжеШчвЛЕФЧПДѓ RTL-to-signoff БЈИцКЭЙмРэЃЌвдМАПЩЖЈжЦЕФЛЗОГ

ЩСЕчаЁБрЫЕУїЃК

дкИпМЖНкЕуЩЯЃЌЙІКФЁЂадФмКЭУцЛ§ (PPA) гыЩшМЦжмзЊЪБМф (TAT) жЎМфДцдкзХЩюПЬЕФГхЭЛЁЃ аТЕФЮяРэКЭЕчЦјЩшМЦЬєеНГіЯжЃЌFinFET ЕШНсЙЙВњЩњСЫаТЕФПМТЧЁЃ ЮЊСЫБЃГжОКељСІЃЌФњВЛФмЖд PPA Лђ TAT НјааШЮКЮШЈКтЁЃ Ншжњ Cadence® Innovus™ ЪЕЪЉЯЕЭГжаПЩгУЕФЬиадКЭЙІФмЃЌФњНЋВЛБиетбљзіЁЃ

Cadence INNOVUS 21.17.000 зюаТАц

Cadence INNOVUS 21.17.000 зюаТАц

Cadence INNOVUS 21.17.000 зюаТАц

Cadence INNOVUS 21.17.000 зюаТАц