Keysight Advanced Design System(ADS)ЦЦНтАцЪЧЙІФмЧПДѓЕФЕчзгЩшМЦздЖЏЛЏШэМўЃЌетПюЭъЩЦЕФИпМЖЩшМЦЯЕЭГЪЙгУПЩАяжњгУЛЇЪЙгУЛљБОаХКХЭъећадЃЈSIЃЉЗжЮіММЪѕЃЌШчблЭМЃЌSВЮЪ§ЃЌЪБгђЗДЩфМЦЃЈTDRЃЉКЭЕЅТіГхЯьгІРДНтОіаХКХЭъећадЮЪЬтЕШЃЌОпгаПьЫйЁЂОЋШЗЁЂМђЕЅвзгУЕФШЋЬзМЏГЩЯЕЭГЁЂЕчТЗКЭЕчДХЗТецЦїЃЌетвтЮЖзХгУЛЇФмЙЛИќПьЫйМђЕЅЕФвЛДЮадОЭЭъГЩгХЛЏЕФзРУцЩшМЦСїГЬЃЌЪЪгУгкЩфЦЕЁЂЮЂВЈКЭаХКХЭъећадгІгУЁЃADS ЪЧЛёЕУЩЬвЕГЩЙІЕФДДаТММЪѕЃЈР§Шч X ВЮЪ§*КЭ 3D ЕчДХЗТецЦїЃЉЕФДњБэЃЌетаЉММЪѕвбБЛЮоЯпЭЈаХгыЭјТчвдМАКНПеКНЬьгыЙњЗРСьгђжаЕФСьЯШГЇЩЬЙуЗКВЩгУЁЃЖдгк WiMAXЁЂLTEЁЂЖрЧЇезЮЛ/УыЪ§ОнСДТЗЁЂРзДяКЭЮРаЧгІгУЃЌADS ФмЙЛНшжњМЏГЩЦНЬЈжаЕФЮоЯпПтвдМАЕчТЗЯЕЭГКЭЕчДХаЭЌЗТецЙІФмЬсЙЉЛљгкБъзМЕФШЋУцЩшМЦКЭбщжЄЁЃБОДЮДјРДЦЦНтАцЯТдиЃЌКЌЦЦНтЮФМўЃЌгаашвЊЕФХѓгбВЛвЊДэЙ§СЫЃЁ

ЙІФмЬиЩЋ

1ЁЂДДаТКЭаавЕСьЯШЕФЗТецММЪѕ

•ЯпадЦЕгђЗТецЦї

•аГВЈЦНКтЗЧЯпадЦЕгђЗТецЦї

•XВЮЪ§ЗЂЩњЦїФЃФтЦї

•ЕчТЗАќТчЛьКЯЪБгђ/ЦЕгђЗЧЯпад

ФЃФтЦї

•ЫВЬЌ/ОэЛ§ЪБгђФЃФтЦї

•аХКХЭъећадЭЈЕРФЃФтЦї

•Keysight TechnologiesЃЌIncЁЃЭаРеУмЯЕЭГФЃФтЦї

•Momentum 3DЦНУцЕчДХФЃФтЦї

•гаЯодЊШЋ3DЕчДХФЃФтЦї

2ЁЂЦфЫћФЃФтММЪѕ

•гХЛЏМнЪЛВе

•RFЯЕЭГФЃФтЦїЃЈдЄЫуЃЉ

•ЫВЬЌИЈжњаГВЈЦНКт

•ЕчТЗЯЕЭГаЭЌЗТец

•Circuit-EMаЭЌЗТецКЭгХЛЏ

•ЭГМЦЗжЮіКЭЩшМЦЃЈУЩЬиПЈТхЃЌDFMЃЌВњСПЗжЮіКЭ

гХЛЏЃЉ

•ДјЙтЦзЕФМЏГЩSpectrasysЯЕЭГФЃФтЦї

ДЋВЅКЭИљБОдвђSpectrasysЗжЮі

3ЁЂЦфЫћВМОжЙІФм

•дРэЭМ/ВМОжЩшМЦЭЌВН

•ЕчЦјЙцдђМьВщ

•дРэЭМ/ВМОжЩшМЦБШНЯ

•ЮяРэСЌНгМьВщЦї

•АќзАХфЙЄОп

4ЁЂЪ§ОнЯдЪОЙІФм

•64ЮЛ

•ЬьЯпЭМ

•ЖрвГ

•Ъ§ОнМЏ

•ЗНГЬЪН

•Ъ§ОнЯдЪОвЧЦїFrontPanels

5ЁЂЩшМЦСїГЬМЏГЩ

•гыKeysight EMProШЋ3D EMФЃФтЦїКЭ3D EMМЏГЩ

•гыMentor BoardstationЕФСДНг

•гыMentor ExpeditionЕФСДНг

•гыCadence AllegroЕФСДНг

•гыCadence VirtuosoЕФСДНг

•гыZuken CR5000ЕФСДНг

•ЭЈЙ§вЕНчСДНгЕНаэЖрЦфЫћPCBЃЌSiPКЭIC EDAЙЄОп

•БъзМKeysight IFFИёЪН

•SPICEФЃаЭЩњГЩЦї

•ПэДјSPICEФЃаЭЩњГЩЦї

•SPICEФЃаЭЕМШы

•Verilog-A

•зщМўПтЙЙНЈЦї

6ЁЂДњЙЄжЇГж

•Global Communication SemiconductorsЃЌIncЁЃ

•IBMАыЕМЬхНтОіЗНАИ

•IHP Microelectronics

•OMMIC

•TowerJazz Semiconductor

•TriQuintАыЕМЬх

•СЊКЯЕЅЦЌАыЕМЬхЃЈUMSЃЉ

•WINАыЕМЬхЙЋЫОЕШЕШ......

7ЁЂзщМўПтжЇГж

MurataЃЌGaAs FETФЃаЭЃЌRoot FETЃЌCurticeЃЌStatzЃЌEEFET3ЃЌ

EEHEMTЃЌGaAsЫЋМЋЃЌKeysight HBTЃЌSilicon BJTаЭКХЃЌ

Gummel-Pool BJTЃЌEEBJT2ЃЌPhillips MEXTRAMЃЌVBICЃЌSilicon

MOSFETФЃаЭЃЌRoot MOSЃЌBSIM 3ЃЌBSIM 4ЃЌUCB MOS 2.3ЃЌ

ЗЩРћЦжMOSФЃаЭ9

8ЁЂНєДеаЭКХ

HICUMЃЌPSPЃЌAngelov GaNФЃаЭЃЌHiSiMЃЌRootФЃаЭ

9ЁЂвЧЦїМЏГЩКЭСЌНгНтОіЗНАИ

•СЌНгЙмРэЦї

•ЪИСПаХКХЗжЮівЧЃЈVSAЃЉ/БљДЈМЏГЩ

•ЪЧЕТПЦММКЭЦфЫћВтЪдЩшБИжЦдьЩЬ

10ЁЂвдгІгУЮЊжааФЕФЩшМЦжИФЯ

•ЙІТЪЗХДѓЦїЩшМЦжИФЯ

•Load Pull DesignGuide

•Й§ТЫЦїЩшМЦжИФЯ

•ЫјЯрЛЗЩшМЦжИФЯ

•ЮодДЕчТЗЩшМЦжИФЯ

11ЁЂЮоЯпБъзМПт

HSPAЃЌ3GPP-LTEЃЌWiMediaЃЌЙЬЖЈWiMaxЃЌвЦЖЏWiMaxЃЌ3GPP

FDD W-CDMAЃЌDTMB / CMMBЃЌCDMAЃЌCDMA-1xEVЃЌCDMA2000ЃЌ

Ъ§зжЕчЪгЃЈDTVЃЉЃЌEDGEЃЌGSMЃЌTD-SCDMAЃЌWLAN

ЦНЬЈ/ВйзїЯЕЭГжЇГж

Windows XPЃЌWindows VistaКЭWindows 7 ProfessionalЃЌSun SolarisЃЌ

RedHatЃЌSuSe

12ЁЂИпадФмКЭЗжВМЪН/ВЂааЗТец

•64ЮЛжЇГжЃЈЖЏСПЃЌЪ§ОнЯдЪО/Ъ§ОнМЏЕШЃЉ

•ЖрЯпГЬжЇГжЃЈЖЏСПЕШЃЉ

•ВЂСЊ/ЗжВМЪНЃЈЖЏСПЃЌЯпадЃЌаГВЈЦНКтЕШЃЉ

•GPUгВМўМгЫйЃЈЫВЬЌОэЛ§ФЃФтЦїЕШЃЉ

13ЁЂЦНЬЈЖЈжЦЭЈЙ§......

гІгУГЬађРЉеЙгябдЃЈAELЃЉ

ЩшМЦжИФЯПЊЗЂШЫдБЕФЙЄзїЪв

ЭаРеУмећКЯ

MatlabЃЌC ++ЃЌSystemC

14ЁЂЦфЫћжївЊЙІФм

•ИпМЖбщжЄФЃаЭЃЈAVMЃЉ

•Momentum RFФЃЪНЃЌMeshersЃЌSolversЃЌИпМЖФЃаЭ

15ЁЂзїЧњМвЃЈAMCЃЉ

•RFжЊЪЖВњШЈБрТыЦї

•жЧФмSIM UI

•ВтЪдЬЈ

•TestLabs

•Еїећ

•ЮоЯпбщжЄ

ЪЙгУЫЕУї

1ЁЂMMICЩшМЦШЫдБ

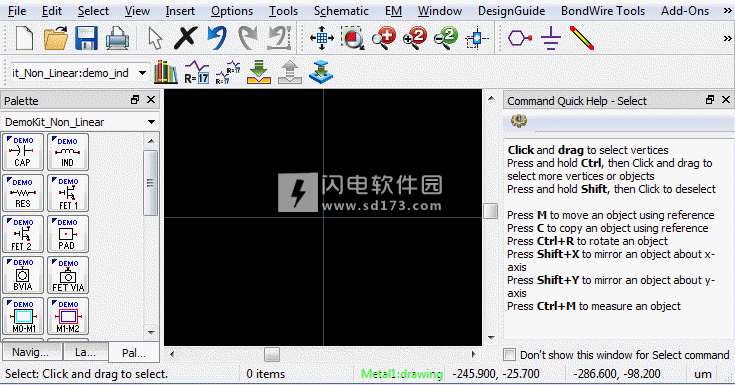

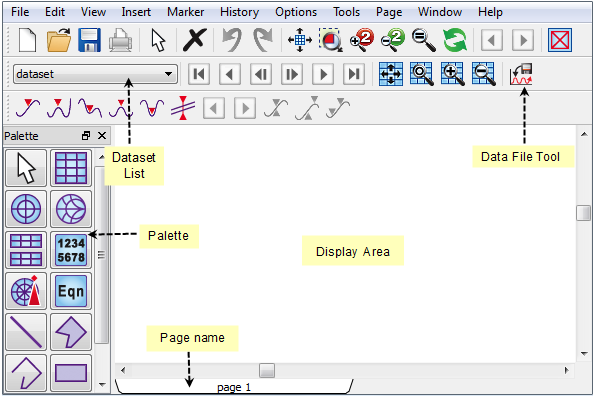

ЮЊСЫЪЙMMICЩшМЦШЫдБФмЙЛНЕЕЭГЩБОВЂПьЫйНјШыЪаГЁЃЌЪзЯШЃЌADSЬсЙЉвЕНчСьЯШЕФЕчТЗКЭЕчДХЗТецЦївдМАЭъећЕФжЦдьСїГЬЁЃADS MMICзРУцСїГЬАќРЈВМОжЃЌДњЙЄГЇКЯИёЧвжЇГждіЧПаЭPDKЃЌMMICЙЄОпРИАќКЌШЋЬзВМОжБрМУќСюЃЌADSзРУцDRCЃЌADSзРУцLVSвдМАЖдAssuraКЭTriQuint mailDRCвдМАMentor Calibre LVSЕФжЇГжЁЃгаЙиKeysightНтОіЗНАИЕФвЛАуаХЯЂЃЌЧыВЮдФMMICЩшМЦЁЃ ADSжаЕФMMICЩшМЦ

2ЁЂаХКХЭъећадЙЄГЬЪІ

аХКХЭъећадЙЄГЬЪІе§дкПЫЗўЖрЧЇезЮЛ/УыЕФЦСеЯЃЌбАЧѓADSвде§ШЗДІРэЪЇецЃЌЪЇХфКЭДЎШХЕШИпЫйаЇгІЁЃЖРЬиЕФЪЧЃЌADSМЏГЩСЫОЋШЗЕФЯЕЭГЃЌЕчТЗКЭEMЗТецЦїЃЌвђДЫФњВЛНіПЩвдЛёЕУе§ШЗЕФД№АИЃЌЛЙПЩвдЭЈЙ§БмУтдквЛзщЕуЙЄОпжЎМфШнвзГіДэЧвКФЪБЕФЪ§ОнДЋЪфРДМгПьЫйЖШЁЃСЂМДЦРЙРADSЃЌСЫНтCiscoЃЌNVIDIAКЭInphiЕШЙЋЫОЗЂЯжЕФЧщПіЁЃгаЙиKeysightНтОіЗНАИЕФвЛАуаХЯЂЃЌЧыВЮдФаХКХЭъећадЗжЮіЁЃ ADSЪ§ОнЯдЪОжаЕФблеж

3ЁЂRFICЩшМЦШЫдБ

ШчЙћФњЕФЩшМЦЛљгкCadenceЩшМЦСїГЬЃЌФњПЩвдЪЙгУKeysightЕФGoldenGate RFICЗТецШэМўжБНгДгCadenceЛЗОГжаЗУЮЪKeysightЧПДѓЕФЦЕгђЗТецММЪѕЁЃРДздCadenceЛЗОГЕФЕчТЗЭјБэвВПЩвдЪЙгУЖЏЬЌСДНгНјШыADSНјааЯЕЭГМЖЗжЮіЁЃЮоТлФФжжЗНЪНЃЌФњЖМгаФмСІгааЇЕиЩшМЦОпгаИпадФмКЭИпВњСПЕФRFICЃЌвдГфЗжРћгУЪаГЁЛњЛсЁЃгаЙиKeysightНтОіЗНАИЕФвЛАуаХЯЂЃЌЧыВЮдФRFICЩшМЦЁЃ RFICЩшМЦ

4ЁЂЩфЦЕКЭЮЂВЈЕчТЗАхЩшМЦШЫдБ

ВЛЖЯдіМгЛљАхВуЪ§ЃЌИќаЁЕФЭтаЮГпДчЃЌИДдгЕФЗтзАММЪѕвдМАИќНєУмЕФЩшМЦНгНќЖШЃЌЪЙRF / MWЕчТЗАхЩшМЦБфЕУИќОпЬєеНадЁЃADSЬсЙЉМЏГЩЕФЯЕЭГЃЌЕчТЗКЭEMЗТецЦїЃЌВМОжКЭЧПДѓЕФгХЛЏЦїЃЌгажњгкЬсИпЩњВњТЪКЭаЇТЪЃЌдкжЦдьжЎЧАбщжЄИпВњСПЩшМЦЁЃADSгыMentorКЭCadenceЕШПђМмМЏГЩВњЦЗХфКЯЪЙгУЃЌвдЪЪгІФњЕФЩшМЦСїГЬЁЃгаЙиKeysightНтОіЗНАИЕФвЛАуаХЯЂЃЌЧыВЮдФRFКЭЮЂВЈАхЩшМЦЁЃ ЩфЦЕКЭЮЂВЈАхЩшМЦ

5ЁЂRFЯЕЭГМЖЗтзАКЭRFФЃПщЩшМЦЦї

ADSЬсЙЉМЏГЩЕчТЗЃЌЯЕЭГКЭ3D EMЗТецЦїЃЌгУгкЩшМЦКЭбщжЄИДдгЕФSiPКЭSoPЩшМЦЃЌШчRFЧАЖЫКЭЙІТЪЗХДѓЦїФЃПщЁЃADSгааЇЕиНтОіСЫЕЭГЩБОЗтзАжаИќаЁЭтаЮГпДчКЭИќЖрЙІФмЕФЧїЪЦЃЌзМШЗЕиНтЪЭСЫRFЛьКЯаХКХЃЌЛьКЯММЪѕзщМўЃЈШчMMICЃЌRFICЃЌЗжСЂдЊМўЃЌЬьЯпКЭДјгаЧЖШыЪНЮодДдЊМўЕФЖрВуЗтзАЃЉЕФНЛЛЅЁЃЗћКЯADSаавЕБъзМЕФЮоЯпПтПЩвдИљОнзюаТЕФЮоЯпБъзМбщжЄЩшМЦЁЃгаЙиKeysightНтОіЗНАИЕФвЛАуаХЯЂЃЌЧыВЮдФRFЯЕЭГМЖЗтзАКЭRFФЃПщЩшМЦЁЃ RFЯЕЭГМЖЗтзАКЭRFФЃПщЩшМЦ

6ЁЂЕчСІЕчзгЩшМЦЪІ

ЯжДњПЊЙиЦїМўЃЈШчSiCКЭGaNЃЉЕФПьЫйБпдЕашвЊЖдEDAЙЄОпНјаааТЕФЫМПМЁЃДЋЭГЕФSPICEВЛзуЃЌвђЮЊЫќНіЯогкЪБгђКЭМЏзмдЊЫиЁЃADSЃЈПЩбЁХфEMProЃЉЬсЙЉМЏзмКЭЗжВМЪНдЊМўЕФЪБгђКЭЦЕгђЗТецЁЃЦЕгђгЩADSЕФаГВЈЦНКтЃЈHBЃЉФЃФтЦїИВИЧЁЃHBбИЫйВњЩњЮШЬЌНтЁЃЮвУЧЕФEMГЁНтЫуЦїЃЌMomentumЃЌFEM ElementКЭFDTD ElementКИЧСЫЗжВМЪНаЇЙћЁЃНЋEMГЁНтЫуЦїгІгУгк“ащФтдаЭ”гаШ§ИіжївЊдвђЃК

PCBзпЯпКЭЙ§ПзЛсЮЊЕчТЗдіМгЯдзХЕФМФЩњзшПЙ

ДДНЈЛљгкEMЕФЗжВМЪНзщМўФЃаЭЃЌР§ШчДјгаМЏГЩДХадЕФPCBзпЯпЕчИаЦї

дк“ащФтЧЛЪв”жаНЈФЃEMI / EMC

ADS2024ЙІФм

аТЕФ PathWave ADS 2024 ЩшМЦЙІФмАќРЈЃК

- ИќПьЕФЕкЖўДњ 3D-EM КЭ 3D-ЦНУцЭјИёЛЎЗжКЭЧѓНтЦї – РћгУгаЙиЮЂВЈНсЙЙКЭЙ§ГЬЕФСьгђжЊЪЖЬсЙЉЫуЗЈдіЧПЁЃЭјИёгХЛЏвдМАВМОжКЭСЌНгИФНјПЩМѕЩйЮЪЬтДѓаЁЃЌДгЖјМгПьЗТецЫйЖШЁЃЧѓНтЦїдіЧПЙІФмЛЙПЩвдНЋЗТецЫйЖШЬсИпЖрДя 10 БЖЃЌВЂЧвашвЊВЛЬЋзЈвЕЕФгУЛЇзЈвЕжЊЪЖРДДІРэИќЙуЗКЕФЮЪЬтЃЌАќРЈ 79GHz ЦћГЕРзДяЦЕТЪЯТЕФКСУзВЈЩшМЦЁЃПЊЗХЪНЙЄзїСїПЩНкЪЁЪ§ОнПтЙмРэЃЌВЂМѕЩйЕќДњЪжЖЏЩшжУЕФПЊЯњЁЃ

- ИпМЖВМОжКЭбщжЄЙІФм – жЇГжжБНгДг LVSЁЂLVLЁЂDRC КЭ ERC ЕФ LDS FOR MIC ЩшМЦЧЉКЫЃЌВЂМђЛЏФЃПщКЭЖрММЪѕзАХфЕФЩњВњСІЁЃWavetekЪЧзюаТвЛМвЭъШЋжЇГжADSНјааЖЫЕНЖЫЙЄзїСїГЬЕФж§дьГЇЁЃ

- ЕчШШдіЧПЙІФмПЩМгЫйбщжЄ – ЭЈЙ§бщжЄВЛЭЌЦЋжУКЭВЈаЮЬѕМўЯТЕФЖЏЬЌЦїМўЙЄзїЮТЖШЃЌЬсИпПЩППадКЭдЫааадФмЁЃЪЙгУ W100E ЕчШШЖЏЬЌжигУжЇГжИпадФмМЦЫуМгЫйКЭИпДя 3051 БЖЕФЫВЬЌМгЫйЃЌДгЖјдкЩшМЦНзЖЮЪЕЯжИќИпЕФВтЪдМЦЛЎИВИЧТЪКЭИќдчЕФМћНтЁЃ

- ЭЈЙ§РЉеЙЕФ Python API жЇГжздЖЈвхЙЄзїСї – ЬсИпСщЛюадКЭПЩРЉеЙадЁЃУцЯђ 5G ЙІТЪЗХДѓЦїЩшМЦШЫдБЕФИКдиЧЃв§Ъ§ОнЕМШыЪЕгУГЬађЁЂANN НЈФЃКЭ Python здЖЏЛЏНХБОЪЭЗХСЫаТЕФгІгУЧБСІЃЌвдДДНЈ ADS ЕФФПБъИіадЁЃ

вЛЁЂЩшМЦгыММЪѕЙмРэ

1ЁЂвЛАу

ИФНјЕФВЮПМЫбЫїКЭЯдЪОЁЃ “НтЪЭ”ВЮПМЮФЯзУшЪіВЂЯдЪОСЫВЮПМаХЯЂЃЌгУгкНтЪЭПтКЭЩшМЦжаЕФЙиЯЕЁЃ ЧыВЮдФВЮПМКЭМвЪєЁЃ

ИФНјСЫПтЪгЭМКЭИДжЦЮФМўжаЕФЪ§ОнЮФМўжЇГжЁЃ

2ЁЂЪ§ОнЯдЪО

ЬэМгСЫЪ§ОнЯдЪОБэДяЪНЙмРэЦїЃЌгУгкБрМЃЌВщевКЭ/ЛђЬцЛЛЗНГЬЪНВЂЕМГіВтСПЗНГЬЪНЁЃ

дкЪ§ОнЯдЪОжаВщевЗНГЬКЭИњзйвРРЕЯюЁЃ гаЙиИќЖраХЯЂЃЌЧыВЮдФВщевДгЪєЗНГЬЪНЁЃ

Ъ§ОнЯдЪОадФмИФНјЁЃ

3ЁЂЪ§ОнСДНгЃЈPythonНгПкЃЉ

Ъ§ОнСДНгЙІФмПЩгУгкВтСПЗНГЬЪНЁЃ гаЙиИќЖраХЯЂЃЌЧыВЮдФдкADSжаЬэМгЪ§ОнСДТЗЙІФмЁЃ

ЖўЁЂЩшМЦБрМ

ВМОждМЪјЪ§ОнПтЪЧЖЈвхВМОжЩшМЦдМЪјЕФжааФЮЛжУЃЌР§ШчМЃЯпПэЖШЃЌЭЈЙ§ЦєЖЏКЭЭЃжЙВувдМАВМЯпМфЯЖЁЃ ВМОждМЪјЪ§ОнПтЕФГѕЪМАцБОЪЕЯжСЫСНжжРраЭЕФдМЪјЃКЧхГ§дМЪјКЭViaдМЪјЁЃ гаЙиИќЖраХЯЂЃЌЧыВЮдФВМОждМЪјЪ§ОнПтЁЃ

ЪЙгУPadstackФЃАхЖЈвхКЭВхШыPCBЙ§ПзКЭКИХЬЁЃ

Ш§ЁЂЕчТЗЗТец

1ЁЂвЛАу

ЛљгкЛЗТЗдівцЕФЮШЖЈадЗжЮіЁЃгаЙиИќЖраХЯЂЃЌЧыВЮдФWSProbeЃЈWinslow Stability ProbeЃЉЁЃ

жЇГжSystemVue 2018 update1.0КЭзюаТЕФ5GNRгУгкЕїжЦаХКХЁЃгаЙиИќЖраХЯЂЃЌЧыВЮдФбщжЄВтЪдЬЈЃЈVTBЃЉЁЃ

УЛгаЪ§ОнСїФЃФтЦїЕФжБНгEVMМЦЫуЁЃгаЙиИќЖраХЯЂЃЌЧыВЮдФEVMМЦЫуЁЃ

ФЃФтЭЫЛ№гХЛЏжЇГжРыЩЂБфСПВЂЧвОпгаИФНјЕФадФмЁЃгаЙиИќЖраХЯЂЃЌЧыВЮдФФЃФтЭЫЛ№гХЛЏГЬађЁЃ

2ЁЂЕчШШ

ЪЙгУОпгаЗЧЭЌВНВуДЮНсЙЙЕФЩшМЦЁЃгаЙиИќЖраХЯЂЃЌЧыВЮдФЪЙгУОпгаЗЧЭЌВНВуДЮНсЙЙЕФЩшМЦЁЃ

ПЩвдЪЙгУeth.cfgЮФМўдЄЯШХфжУЕчШШПижЦЦїФЌШЯжЕЁЃгаЙиИќЖраХЯЂЃЌЧыВЮдФЩшжУETHПижЦЦїЕФФЌШЯжЕЁЃ

Beta - ETHЕчТЗАќТчФЃФтдЪаэжИЖЈШЮвтЭЌВНЪБМфБэЃЈМДШЮвтЪБМфВНГЄзїЮЊЪБМфЕФКЏЪ§ЃЉЃЌгыжЎЧАЕФЭГвЛЛђЖдЪ§НјеЙаЮГЩЖдБШЁЃ

гаЙиЪЙгУШЮвтЪБМфВНГЄЕФИќЖрЯъЯИаХЯЂЃЌЧыВЮдФФЃФтЦїЪБМфВНГЄВПЗжжаЕФВЮЪ§ЁЃ

3ЁЂЖїжЧЦжSiMKitаЭКХ

етаЉФЃаЭвбИќаТЮЊSiMKit ReleaseЃЌЯждкетаЉЖМЪЧФЌШЯАцБОЁЃ

гаЙиИќЖраХЯЂЃЌАќРЈжЇГжЕФЩшБИАцБОЃЌЧыВЮдФЩшБИКЭаЭКХЃЌNXP SiMKitЁЃ

ЫФЁЂHSDЩшМЦ

1ЁЂвЛАу

ЖгСаЙмРэЦїЃЈQMЃЉЙмРэADSжаЕФВтЪдЦНЬЈ/ЙЄзїЬЈЁЃ гаЙиИќЖраХЯЂЃЌЧыВЮдФЖгСаЙмРэЦїЁЃ

2ЁЂДЎааНтДЎЦї

CTLE VisualizerЁЃ гаЙиИќЖраХЯЂЃЌЧыВЮдФCTLEОљКтВЮЪ§ЁЃ

ЭЈЙ§ЮЊOIF CEI-28GЬсЙЉЕФдЄЩшЃЌИќЧсЫЩЕиНјааCTLEЩшжУЁЃ CEI-56G-VSRЃЌIEEE 802.2bs CDAUI8ЃЌPCIeКЭUSB Gen3ЁЃ

ЯдЪОЦЕТЪЯьгІЃЌЗљЖШКЭЯрЮЛЁЃ

жЇГжгУЛЇЬсЙЉЕФдЄЩшЁЃ

ЪЙгУCTLEдіЧПMIPI C-PHYНгЪеЦїЁЃ гаЙиИќЖраХЯЂЃЌЧыВЮдФRx_CphyЃЈMIPI C-PHYНгЪеЦїЃЉЁЃ

FlexDCA_ProbeСЌНгдіЧПЙІФмЃЌЪЪгУгкдЖГЬH / WКЭдЖГЬPCЁЃ гаЙиИќЖраХЯЂЃЌЧыВЮдФFlexDCA ProbeЁЃ

COMЃЈЧўЕРгЊдЫБЃжЄН№ЃЉЁЃ гаЙиИќЖраХЯЂЃЌЧыВЮдФMatlabдЫааЪБжЇГжЁЃ

Linux MatlabдЫааЪБжЇГжЁЃ

COM 2.6КЭMatlab R2018bжЇГжЁЃ

жЧФмблЬНЭЗЃКДјгаДЅЗЂблЭМЕФЖрЭЈЕРжЇМмЁЃ гаЙиИќЖраХЯЂЃЌЧыВЮдФжЧФмблЬНеыЁЃ

3ЁЂDDR/ФкДц

ФкДцЩшМЦЦїЕФDDRSetup

еыЖдDDRЩшМЦЕФЩшжУSIProЗТецЕФИФНј

ЪЙгУСїГЬИФНјSIPro-> Memory Designer

DDR PackageзщМўЃЌгУгкжИЖЈВЛЪєгкIBISЮФМўЕФШэМўАќЁЃ гаЙиИќЖраХЯЂЃЌЧыВЮдФDDRАќЁЃ

4ЁЂEM-SI / EM-PI

ЭЈЙ§ЩшМЦЪІ

ЖрРЁЫЭЙ§Пз

ЮЂЙ§ПзКЭНЛДэЙ§Пз

ЕМГіЕНВМОж

ГіПкЕНEMPro

ЭЈЙ§ЭМВуЖЈжЦЦДНг

SIProЕФВЂааЗТецЙЄзї

ОжВПВЂааФЃФт

МЏШКЩЯЕФВЂааФЃФтзївЕ

зщМўФЃаЭжЦзїЦї

PCBЕМШыЩњГЩФЃаЭгГЩфЮФМў

ФЃаЭгГЩфЮФМўЮЊгУЛЇбЁдёЕФзщМўЩњГЩдРэЭМКЭЗћКХ

ПЩвдБрМФЃаЭгГЩфЮФМўвджИЯђЙЉгІЩЬПтКЭздЖЈвхФЃаЭ

ЪЙгУLib CellКЭSnPзщМўНјааPIPro DeCapгХЛЏ

PIProЖрв§НХДг1ИіНгЪеЦїВ№ЗжЕНЖрИіНгЪеЦїв§НХЖд

PIProЖрв§НХОЋЖШИФНј

ЕШЕчСїКЭЕШЕчбЙЯждкЕМжТНЯЕЭЕФзшПЙКЭИФЩЦЕФЕчСїЗжВМЁЃ

АќзАЕМШыЕНPIProЕФADFIЕМГі

здЖЈвхADFIЩшжУЃЌгУгкДгCadence SiPКЭMCMЕМГіАќЃЌгУгкSIPro / PIProЁЃ

PIProеыЖдЕчСїФЃЪНКЭЕчбЙФЃЪНAC EMФЃаЭНтОіЗНАИИФНјСЫЖрв§НХЗжзщКЭШЁЯћЗжзщЙІФмЁЃ

дка§зЊ/ЦНвЦ/ЫѕЗХЦкМфИќПьЕифжШОДѓаЭЩшМЦЁЃдкетаЉВйзїЦкМфЃЌфжШОМѕЩйЕФМИКЮЯИНквдБЃГжПЩНгЪмЕФжЁЫйТЪЁЃ

ЮхЁЂEMФЃФт

1ЁЂRFPro

гУЛЇЖЈвхЕФEMЬсШЁЗжЮідЪаэEMФЃФтбЁЖЈЭјТчКЭДѓаЭЩшМЦзщМўЕФзщКЯЁЃ

гыFEMВЂааФЃФтЦЕТЪЃЈдкБОЕижїЛњЩЯЛђЬсНЛЕНМЏШКЖгСаЃЉКЭMomentumЃЈНіжЇГжЬсНЛЕНМЏШКЖгСаЕФзївЕЃЉЁЃдкAnalysis→бЁЯю→зЪдДбЁЯюПЈжажИЖЈВЂаазївЕЕФЪ§СПЁЃ

ДДНЈаТЕФRFProЪгЭМЪБЃЌПЩвдбЁдёLTDЛљАхЮФМўЁЃ

дкЛљВФБрМЦїЃЈ.substЛђ.ltdЃЉжаДђПЊRFProжаЕФВМОжЪБЃЌжИЖЈвЊХХГ§ЛђАќКЌЕФЭМВугУЭОЁЃ

ЩЯЯТЮФВЫЕЅвбЬэМгЕНв§НХЃЌдЪаэдкЭМВуЩЯДДНЈащФтв§НХЁЃ

SВЮЪ§→СэДцЮЊЖдЛАПђгавЛИіаТБъжОЃЌгУгкдкНЋSВЮЪ§ЕМГіЕНЪ§ОнМЏКѓДђПЊЪ§ОнЯдЪОДАПкЁЃ

ДДНЈНХБОЩЯЯТЮФВЫЕЅбЁЯювбЬэМгЕНЗжЮіжаЃЌдЪаэФњНЋЗжЮіЩшжУДЋЪфЕНСэвЛИіЪгЭМЁЃИУНХБОЛЙПЩвдзїЮЊбЇЯАШчКЮЭЈЙ§pythonНХБОЖЈвхЗжЮіЕФЦ№ЕуЁЃ

дка§зЊ/ЦНвЦ/ЫѕЗХЦкМфИќПьЕифжШОДѓаЭЩшМЦЁЃдкетаЉВйзїЦкМфЃЌфжШОМѕЩйЕФМИКЮЯИНквдБЃГжПЩНгЪмЕФжЁЫйТЪЁЃ

ЭЈЙ§ЩшжУЛЗОГБфСПRFPRO_FEM_GENERATION = 2РДдЄРРЯТвЛДњFEMФЃФтЦїЁЃ ADS 2020АцБОжаЕФ“ЪдгУ”ДњТыПЩвдИќПьЕидЄДІРэЃЈЖрММЪѕЃЉЩшМЦКЭ“ЭјзДгђгХЛЏ”ФЃФтЦїбЁЯюЁЃаТСїГЬПЩгУзїФЌШЯЃЈRFPRO_FEM_GENERATION = 1ЃЉFEMФЃФтЦїЕФЬцДњЗНАИЁЃ

ADS 2020ЗЂВМЪЧPython 2.7ЕФзюКѓвЛИіАцБОЃЌвђЮЊPython 2.7е§дкДяЕНЦфЪйУќжеНсЁЃ ADS 2021АцБОМЦЛЎЪЙгУPython 3.7ЁЃПЩвдЯТдиPython 3.7ЕФЪдгУАцЁЃСЊЯЕММЪѕжЇГжвдЛёЕУНјвЛВНжИЕМ

ADS 2020АцБОЪЧжЇГж32ЮЛАцCadence VirtuosoЕФзюКѓвЛИіАцБОЁЃ ADS 2021МЦЛЎНіжЇГж64ЮЛАцБОЕФCadence VirtuosoЁЃ

2ЁЂEMЩшжУ

ЛљгкEM SetupЕФПЩЛЅВйзїEM-CosimulationСїГЬвбОНтОіСЫвЛИіЮЪЬтЁЃЕБВМОжжаДцдк1x1 OA viaЪ§зщЪБЃЌЪгЭМЩњГЩЪЇАмЁЃ

3ЁЂFEM

ЭјИёЩњГЩадФмКЭЮШНЁадИФНјЁЃ

ЬсИпВЂааЦЕТЪЩЈУшЕФЮШНЁадЁЃ

ЪЙгУ“sitecluster”НЋЖгСазЪдДгГЩфАѓЖЈЕНmaster / mesh / solveНзЖЮЁЃ

4ЁЂЖЏСП

ADS 2019жав§ШыЕФаТЕМЬхЫ№КФФЃаЭЕФACааЮЊЕФЯИЛЏЁЃЕБРлЛ§БпдЕЭјИёКЭКёН№ЪєЪБЃЌЫќПЩФмЕМжТЫцзХЦЕТЪЕФдіМгЖјЙ§ИпЙРМЦЕчзшЁЃДЫЮЪЬтвбЕУЕННтОіЁЃВЛдйЭЦМіЩшжУMOM3D_USE_LOCALTHICKNESS = 0ЕФНтОіЗНЗЈЁЃ

СљЁЂЕчСІЕчзг

ЕчСІЕчзгзЈвЕШЫЪПЃЈPEProЃЉ

гУгкПЊЙиФЃЪНЕчдДЃЈSMPSЃЉЩшМЦЕФЯТвЛДњВМОжКѓEMЕчТЗаЭЌЗТецЦНЬЈЁЃ

гУгкSMPSЩшМЦЕФEMКЭЫВЬЌ/ОэЛ§ФЃФтПижЦЦїЕФздЖЏгХЛЏЩшжУЁЃ

гУгкЕчбЙМтЗхКЭДЋЕМEMIЗжЮіЕФдЄЙЙНЈВтЪдЦНЬЈЁЃ

ЦпЁЂPDKбщжЄЦї

Й§ГЬЩшМЦЬзМўЃЈPDKЃЉValidatorЬсЙЉздЖЏЛЏММЪѕЃЌгУгкЬсЙЉИпжЪСПЃЌЭъШЋЦєгУЕФADS PDKЁЃ

ЪЙгУаТЕФADSАцБОбщжЄPDK

ЦєгУЙІФмЃЈDRCЃЌLVSЃЉ

АЫЁЂЩшМЦЙцдђМьВщЃЈDRCЃЉ

1ЁЂAssura DRC

ЙцдђРрБ№

ИФНјСЫЖдДјПЊЙиЕФЙцдђЮФМўЕФжЇГжЁЃ ЯждкПЩвдздЖЏМьВтПЊЙиЁЃ

2ЁЂADS DRC

ШнСПКЭадФм

ИФНјСЫЖдОпгааэЖрЪфШыВуЕФДѓаЭЙцдђЮФМўЕФжЇГжЁЃ

ЬсИпСЫdve_quadoutЃЈЃЉУќСюЕФаЇТЪ

гАЯьЙцдђжДааЭтВПМфЯЖЙцдђЃЌШЛКѓДгбЁЖЈБпдЕЬсШЁЫФБпаЮЁЃ ЖдгкАќКЌдВаЮФЉЖЫРраЭЕФдВаЮЛђМЃЯпЕФЩшМЦЃЌПЩвдЯдзХЬсИпадФмЁЃ

DRCЮФЕЕ

100ЖрИіШчКЮБраДЙцдђЕФР§згЁЃ

ЧсЫЩВщеваХЯЂЁЃ ЪЙгУ“ЕМКН”УцАхфЏРРЕНЙцдђЁЃ

БраДЩшМЦЙцдђЬсЙЉСЫЫЕУїЙцдђРрБ№КЭСїГЬБфЬхЕФЪОР§ЙцдђЮФМўЁЃ

ИќаТЙцдђгяЗЈвдЯдЪОЫљгажЇГжЕФВЮЪ§ЁЃ Р§ШчЃЌЖрБпаЮбЁдёЙцдђжЇГжЯћЯЂВЮЪ§ЃЌИУВЮЪ§ЬсЙЉИќМђЕЅЕФЙцдђгяЗЈЁЃ

гћЛёЕУИќЖраХЯЂЁЃ ЧыВЮдФЩшМЦЙцдђМьВщЃЈDRCЃЉЁЃ

ОХЁЂЩшМЦЬзМў

ИќаТСЫвдЯТЕФSi-RFIC PDKФЃаЭАќКЌЪЕгУГЬађЃК

“Юо”ЗНАИвбЬэМгЮЊФЌШЯЗНАИжЎвЛЁЃ

ИќаТСЫФЃаЭАќКЌзщМўЃЌФњЯждкПЩвдДгзщМўБОЩэЕїгУЩшжУЖдЛАПђЁЃ

гаЙиИќЖраХЯЂЃЌЧыВЮдФSi RFIC PDKФЃаЭАќКЌЪЕгУГЬађЁЃ

ДгADS 2020АВзАГЬађжаЩОГ§СЫвдЯТОЩАцКЭОЩАцADSбнЪОЙЄОпАќЃК

DEMOKIT

DemoKit_V3

SampleKit

eesofDemoKit

ФњПЩвдДгжЊЪЖжааФЯТдиЩЯУцСаГіЕФЩшМЦЙЄОпАќЃЌНігУгкДЋЭГФПЕФЁЃ ЪЙгУетаЉОЩЬзМўЕФШЮКЮХрбЕФЃПщЖМашвЊЪЙгУзюаТЕФADSЗЧЯпадбнЪОЬзМўНјааИќаТЁЃ

ИќаТСЫвдЯТADSЗЧЯпадбнЪОЬзМўЃК

ЫљгаDSNВЮПМОљвбДгЩшМЦЙЄОпАќжаЩОГ§ЁЃ

аТЕФЛљАх“demo_modified.subst”діМгСЫВФСЯЕчЕМТЪЕФЪЕгУжЕЃЌвдКЯГЩИќецЪЕЕФЕчИаЦїЁЃ

ЬэМгCNEXзщМўЖЈвхвджЇГжCalibre LVSКЭAssura LVSЁЃ

ЪЎЁЂбщжЄВтЪдЬЈЃЈVTBЃЉ

ЯждкжЇГжЕЅЖЫПкVTBЃЈНідДЃЉФЃФтЁЃЯждкЃЌФњПЩвддкSystemVueжаДДНЈИДдгЕФЕїжЦдДЃЌВЂгыADS Circuit EnvelopeвЛЦ№ЪЙгУЁЃ

ДгADS 2017ПЊЪМЃЌвЊАВзАVTBЙІФмЫљашЕФЮФМўЃЌФњашвЊЯТдиЕЅЖРЕФVTBАВзАГЬађЃЈНіЪЪгУгкWindowsЃЉЁЃЖдгкLinuxЃЌVTBАВзАГЬађгыADSАВзАГЬађРІАѓдквЛЦ№ЁЃ

НЈвщНЋМцШнЕФADSКЭVTBАВзАГЬађЯТдиЕНЭЌвЛФПТМЁЃЯТдиКѓЃЌдЫааADSАВзАГЬађЁЃДЫЙ§ГЬНЋздЖЏАВзАVTBЙІФмЁЃ

ШчЙћФњвбОАВзАСЫADSВЂЧвЗЂЯжШБЩйVTBЙІФмЃЌФЧУДФњашвЊЯТдиВЂАВзАVTBЁЃ

ADSжаЩ§МЖЕФSystemVue 2018в§ЧцЁЃ

ЬэМгСЫвдЯТаТVTBЃК

5GИпМЖЕїжЦНтЕїЦїЙЄзїЧј

NB IoTЙЄзїЧј

ИќаТСЫЯжгаVTBЕФУћГЦЃК

WLAN 11acЙЄзїЧј

ADS 2019НіжЇГжЕМШыЪЙгУSystemVue 2018КЭSystemVue 2018 Update 0.1ДДНЈЕФздЖЈвхVTBЃЈSystemVueЙЄзїЧјЃЉЁЃ

ЪЎвЛЁЂР§зг

ЪЙгУ“ЪОР§ЫбЫї”ЖдЛАПђПЩвдЫбЫїЫљгааТЬэМгЕФЪОР§ЁЃ

гаЙиИќЖраХЯЂЃЌЧыВЮдФЪЙгУЪОР§ЙЄзїЧјЁЃ

ЪЎЖўЁЂаэПЩ

ADS 2020вЊЧѓЃКaЃЉEEsof EDAаэПЩШэМўЕФ2019.02АцБОЃЌbЃЉзюЕЭДњТызжАцБО2019.02ЛђИќИпАцБОЃЌвдМАcЃЉаэПЩЗўЮёЦїШэМўlmgrdКЭagileesofdЃЌвЊЩ§МЖЕНжСЩйгыАцБОЯрЭЌЕФАцБОEEsof EDAаэПЩШэМў2019.02жаАќКЌЕФФкШнЁЃШчЙћВЛТњзуШЮКЮетаЉвЊЧѓЃЌдђВЛЛсЦєЖЏADS All-VersionsЁЃЧыВЮдФаэПЩжЄДњТызжАцБОМцШнадБэЁЃ

дкEEsof EDAаэПЩжЄЙЄОпАцБО2019.02жаЃЌаэПЩЙЉгІЩЬЪиЛЄГЬађЃЈagileesofdЃЉгыFlexNet FNP 11.13.1.4АцБОЃЈWindowsЃЉКЭFlexNet FNP 11.13.1.3АцБОЃЈLinuxЃЉЕФFlexNetаэПЩжЄЙмРэЦїЪиЛЄГЬађЃЈlmgrdЃЉМЏГЩдквЛЦ№ЁЃЖдгкWindowsЦНЬЈЃЌADSАВзАГЬађНЋФЌШЯЮЊБОЕиНкЕуЫјЖЈаэПЩжЄгУЛЇздЖЏЩшжУетСНИіаТЕФаэПЩжЄЗўЮёЦїЪиЛЄГЬађ;ЖдгкLinuxЦНЬЈЃЌФњашвЊАДееLinux Licensing SetupжИСюЭъГЩаэПЩХфжУЙ§ГЬЁЃгаЙиИќЖрЯъЯИаХЯЂЃЌЧыВЮдФаэПЩЃЈЪЪгУгкЙмРэдБЃЉЁЃ

ЪЎШ§ЁЂвбжЊЕФЮЪЬт

ЩшМЦгыММЪѕЙмРэ

НЋADS 2020гыpycell studio 2018ЃЈPyCell StudioШэМўАќЃКАцБОO-2018.09ЃЉвЛЦ№ЪЙгУПЩФмЛсдкlinuxжеЖЫЩЯЬсЪОOAАцБОВЛЦЅХфОЏИцЯћЯЂЁЃЕЋЪЧЃЌЖдADSжаЕФiPDKСїУЛгагАЯьЁЃ

LinuxжеЖЫЯћЯЂЃК

ЧыЧѓЕФаЁаЭAPIАцБО'518'ЃЌOpenAccess build '22 .50.030'жЇГжЃЌБШOpenAccess build '22 .50.043'ЕФЙВЯэПтЕФДЮвЊAPIАцБО'514'ИќаТЁЃ

гЩгкOpenAccessАцБОВЛЦЅХфЃЌVirtuoso ICАцБО6.1.8ИНДјЕФExpress PcellВхМўЮоЗЈгыADS 2020вЛЦ№ЪЙгУЁЃ

НтОіЗНЗЈЃКдЫааADS 2020ЪБЃЌНЋLD_LIBRARY_PATHЛЗОГБфСПТЗОЖЩшжУЮЊжИЯђICАцБО6.1.7жаЕФФПТМЁЃ

AELГЃСПЪмЕНБЃЛЄЃЌВЛгІдкШЮКЮDDSБэДяЪНжаНјаааоИФЁЃШчЙћЗЂЩњаоИФAELГЃЪ§ЕФГЂЪдЃЌНЋЗЂГіAELДэЮѓЁЃ

Python Datalink

ЪЙгУСЌНгЕНLan InstrumentsЕФConnection Expert 2019ЪБЃЌдкdl_visa_queryЃЈЃЉКЭdl_visa_writeЃЈЃЉЦкМфПЩФмЛсГіЯжДэЮѓЯћЯЂЁЃ

ГЌГіашЧѓЃКЧызЂвтЃЌдкФГаЉЧщПіЯТЃЌПЩФмашвЊХфжУEoDЩшжУВХФме§ШЗЯдЪОSpyderЁЃЧыСЊЯЕФњЕФEoDжЇГжДњБэвдЛёШЁИќЖржИЕМЁЃ

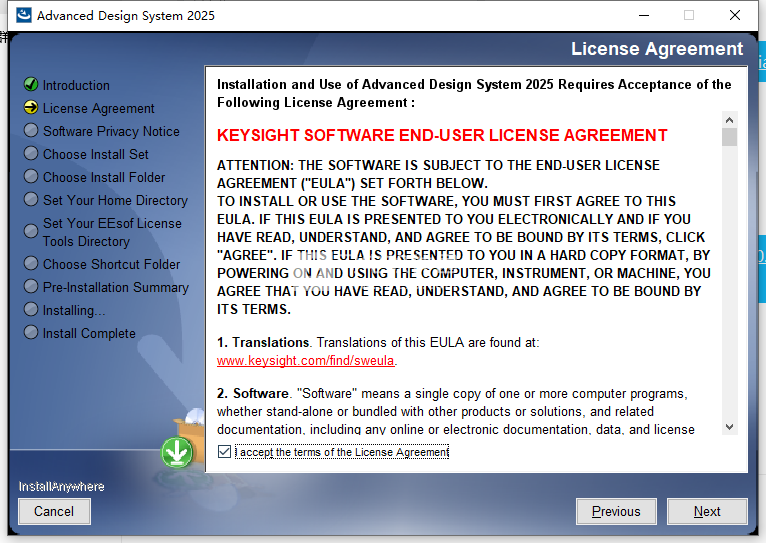

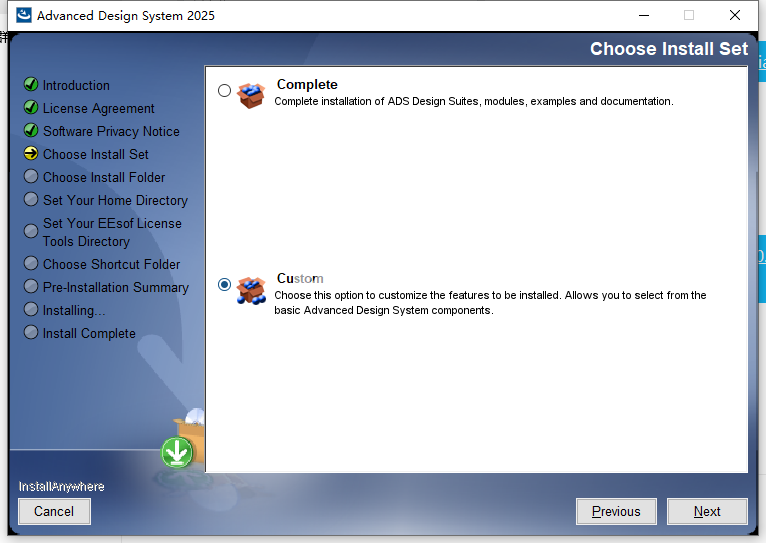

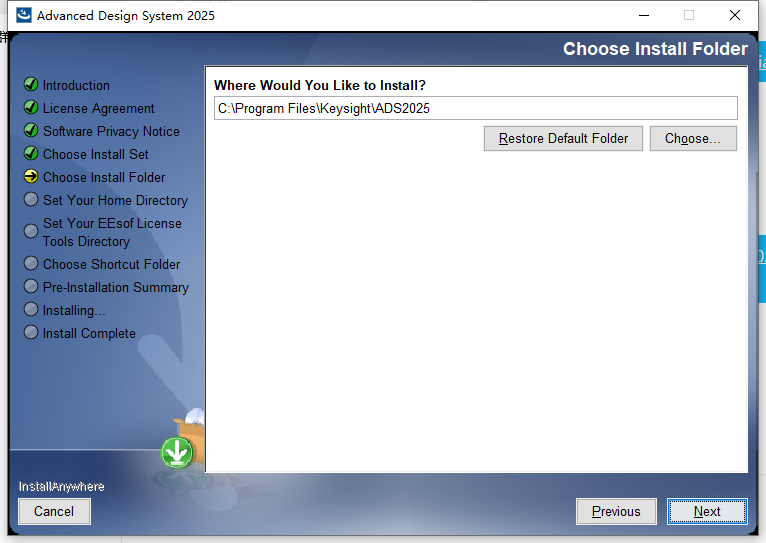

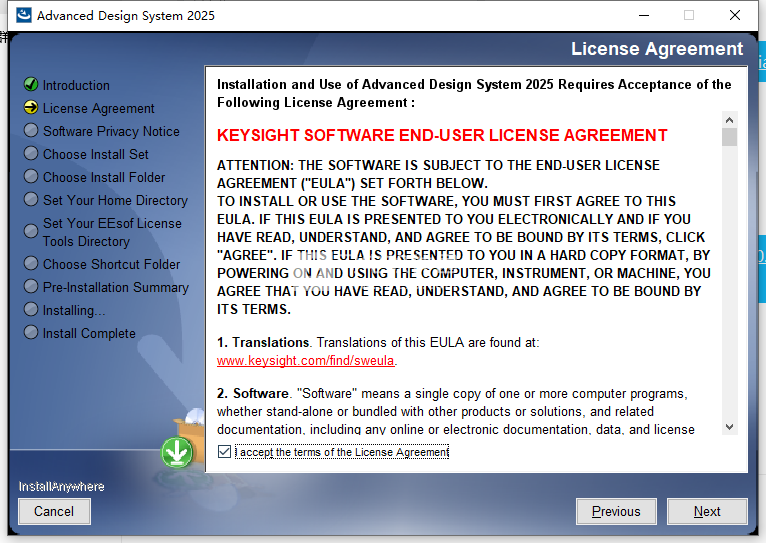

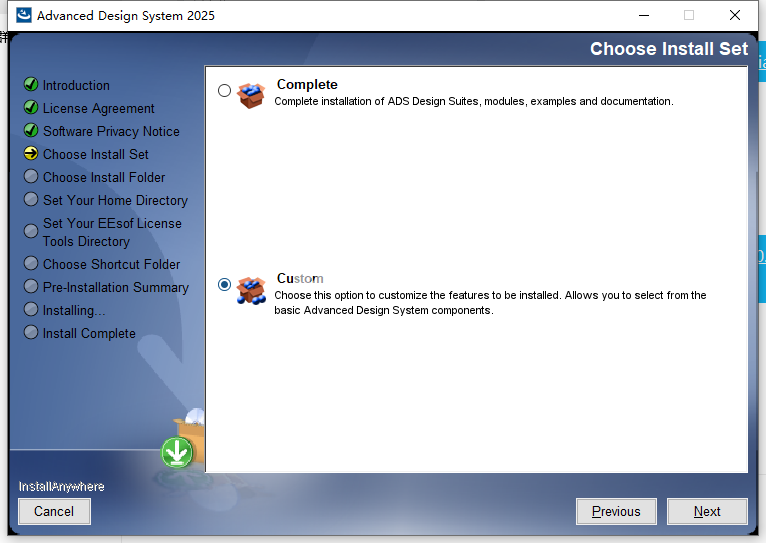

АВзАЦЦНтНЬГЬ

1ЁЂдкБОеОЯТдиВЂНтбЙЃЌШчЭМЫљЪО

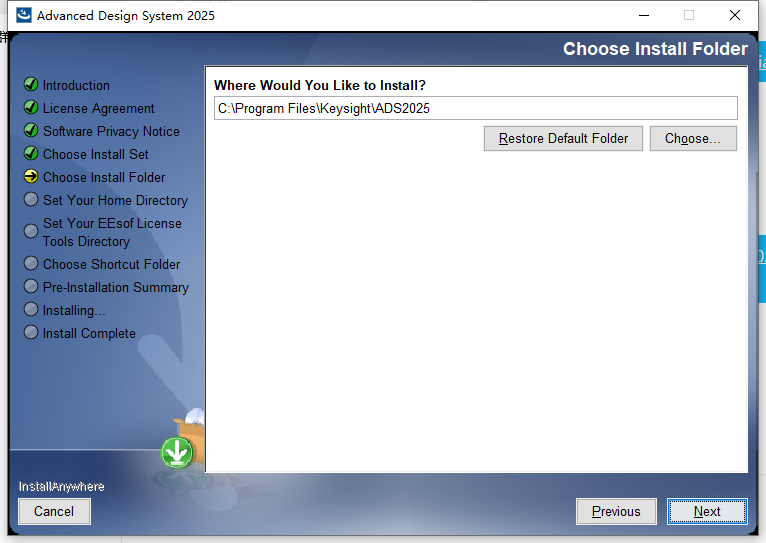

2ЁЂАВзАГЬађЃЌЙДбЁЮвНгЪмавщ

3ЁЂАВзАЩшжУ

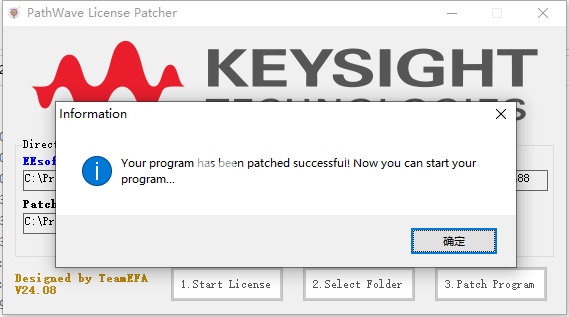

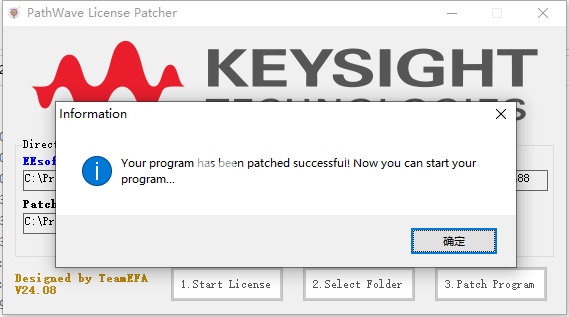

4ЁЂАВзАЭъГЩЃЌЙмРэдБЩэЗндЫааPathWaveLicensePatcher.exeЃЌЕуЛїselect folderЩшжУШэМўАВзАФПТМЃЌЕуЛїpatch

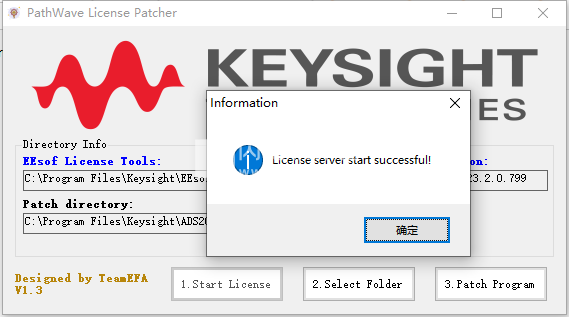

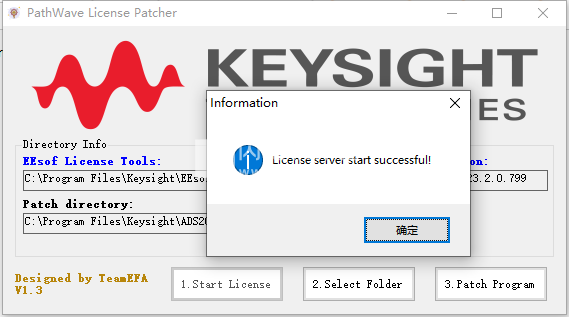

5ЁЂЕШД§ЭъГЩКѓЃЌЕуЛїstart license

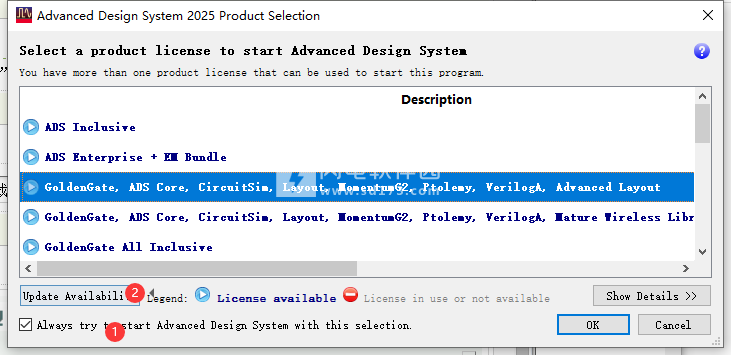

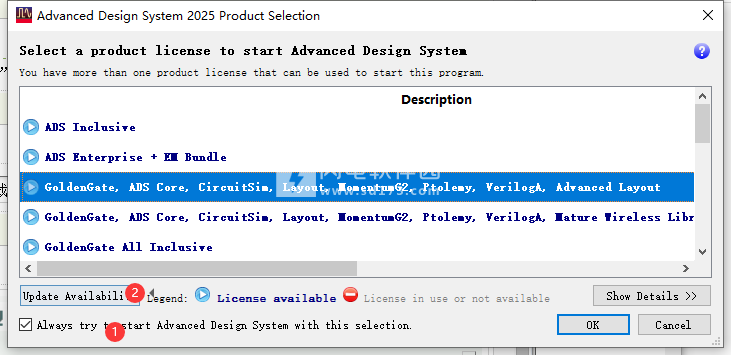

6ЁЂдЫааГЬађЃЌЕуЛїshowеЙЪОаэПЩжЄЃЌбЁдёВњЦЗаэПЩжЄвдЦєЖЏAdvanced Design Systen

ФњгаЖрИіВњЦЗаэПЩжЄПЩгУгкЦєЖЏДЫГЬађЁЃЕуЛїok

ЪЙгУАяжњ

вЛЁЂЗћКХЪгЭМ

вЊДДНЈаТЗћКХЃЌЧыАДеевдЯТВНжшВйзїЃК

ЦєЖЏADSВЂДђПЊЯжгаЙЄзїЧјЛђДДНЈаТЙЄзїЧјЁЃ

дкжїADSДАПкжаЃЌЪЙгУвдЯТШ§ИібЁЯюжЎвЛДђПЊ“аТНЈЗћКХ”ЖдЛАПђЃК

бЁдёЮФМў>аТНЈ>ЗћКХЁЃ

ЕЅЛїЙЄОпРИжаЕФ“аТНЈЗћКХ”АДХЅЃЈЃЉЁЃ

гвМќЕЅЛїЙЄзїЧјУћГЦЃЌШЛКѓбЁдё“аТНЈЗћКХ”бЁЯюЁЃ

Дг“Пт”ЯТРСаБэжаЃЌбЁдёНЋДцДЂаТЗћКХЕФПтУћГЦЁЃ

ЪфШыаТЕЅдЊУћГЦЛђЕЅЛї“фЏРРЕЅдЊ”АДХЅДгЫљбЁПтЕФЯжгаЕЅдЊИёжабЁдёЕЅдЊИёЁЃ

ЕЅЛї“БрМЪгЭМУћГЦ”вдЪЙгУФЌШЯУћГЦДДНЈаТЕФЗћКХЪгЭМЃЌМД“ЪгЭМУћГЦБрМЦї”ДАПкжаЕФ“ЗћКХ”ЛђаТЪгЭМУћГЦЁЃ

ЕЅЛї“ШЗЖЈ”вдДђПЊДДНЈЗћКХЪгЭМЕФЗћКХДАПкЁЃ

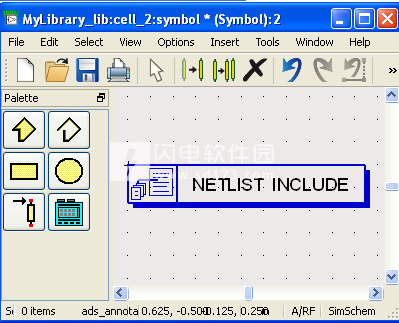

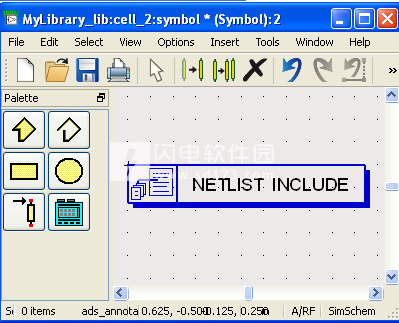

ЯТЭМЯдЪОСЫSymbolЪгЭМЁЃ

ЖўЁЂВМОжЪгЭМ

ЦєЖЏADSВЂДђПЊЯжгаЙЄзїЧјЛђДДНЈаТЙЄзїЧјЁЃ

дкжїADSДАПкжаЃЌЪЙгУШ§ИібЁЯюжЎвЛДђПЊ“аТНЈВМОж”ЖдЛАПђЃК

бЁдёЮФМў>аТНЈ>ВМОжЁЃ

ЕЅЛїЙЄОпРИжаЕФ“аТНЈВМОж”АДХЅЃЈЃЉЁЃ

гвМќЕЅЛїЙЄзїЧјУћГЦЃЌШЛКѓбЁдё“аТНЈВМОж”бЁЯюЁЃ

Дг“Пт”ЯТРСаБэжаЃЌбЁдёНЋДцДЂаТВМОжЕФПтУћГЦЁЃ

ЪфШыЕЅдЊИёУћГЦЛђЕЅЛї“фЏРРЕЅдЊ”АДХЅДгЫљбЁПтЕФЯжгаЕЅдЊИёжабЁдёЕЅдЊИёЁЃ

ЕЅЛї“БрМЪгЭМУћГЦ”вдЪЙгУФЌШЯУћГЦДДНЈаТЕФВМОжЪгЭМЃЌМД“ЪгЭМУћГЦБрМЦї”ДАПкжаЕФ“ВМОж”ЛђаТЪгЭМУћГЦЁЃ

ЕЅЛї“ШЗЖЈ”ЃЌНЋДђПЊВМОжДАПкЃЌФњПЩвддкЦфжаДДНЈВМОжЪгЭМЁЃ

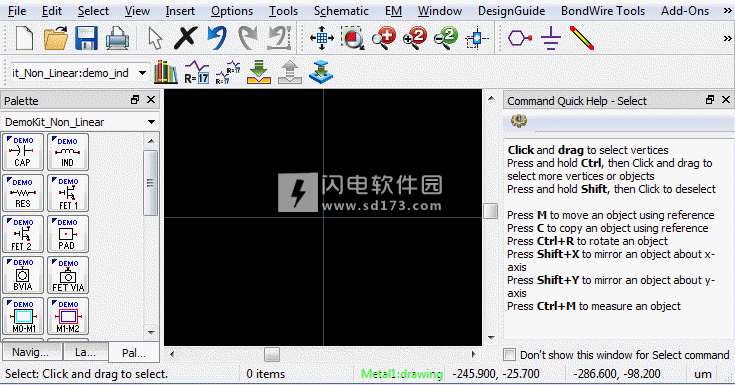

ЯТЭМЯдЪОСЫ“ВМОж”ЪгЭМЁЃ

Ш§ЁЂЪ§ОнЯдЪОДАПк

PathWave Advanced Design System (ADS) Update 2 Win/Linux

PathWave Advanced Design System (ADS) Update 2 Win/Linux

PathWave Advanced Design System (ADS) Update 2 Win/Linux

PathWave Advanced Design System (ADS) Update 2 Win/Linux