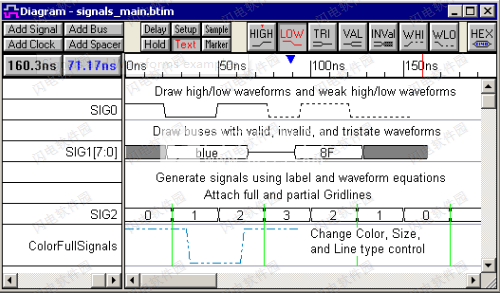

SynaptiCAD Product Suite 20破解版将为电气工程师们快速创建完美的设计,安装完成包含多个实用程序,其中TestBencher代表了HDL测试平台自动化开发中的一项重大突破。 TestBencher Pro为设计人员提供了用于快速生成系统级测试平台的图形环境。 用户绘制时序

SynaptiCAD Product Suite 20破解版将为电气工程师们快速创建完美的设计,安装完成包含多个实用程序,其中TestBencher代表了HDL测试平台自动化开发中的一项重大突破。 TestBencher Pro为设计人员提供了用于快速生成系统级测试平台的图形环境。 用户绘制时序图,然后TestBencher生成本机VHDL,Verilog,OpenVera.e和C ++代码。 生成的代码是模块化的,可以与所有主要的VHDL和Verilog模拟器一起使用。Verilogger Pro是一种新型Verilog仿真环境,将传统Verilog仿真器的所有功能与地球上最强大的图形测试矢量生成器结合在一起。 在Verilogger Pro中,模型测试是如此之快,以至于您可以对设计中的每个模型进行真正的自下而上的测试,而这在市场竞争中通常会被跳过。

WaveFormer Pro通过将时序分析和交互式仿真相结合,可以帮助您更快地设计,减少错误。 快速输入设计的基本元素,而无需创建原理图或HDL模型。 修改设计时,可以即时反馈,从而逐步进行仿真。 从时序图生成VHDL,Verilog,SPICE和码型生成器代码。 导入从逻辑分析仪和VCD文件获取的波形数据。您将只需要安装一次就拥有完整的解决方案,并且安装破解非常简单,安装包中含许可密钥文件,复制到安装目录中即可完成破解!

软件特色

1、以图形方式生成VHDL,Verilog和SPICE测试台

WaveFormer Pro,用于仅用于刺激的测试台

WaveFormer Pro与反应式测试台生成

TestBencher Pro创建基于事务的测试台

SPICE测试台激励(模拟和数字)

2、在Vhdl和Verilog

V2V 之间进行翻译:自己动手翻译工具

全方位服务的VHDL和Verilog翻译:我们为您服务

3、模拟和调试VHDL和Verilog设计

VeriLogger Extreme:高性能Verilog 2001仿真器

BugHunter Pro:适用于所有HDL仿真

器的图形调试器Gigawave Viewer:VCD / SPICE波形查看器动态

门:网表分析器

4、创建和导航Verilog和VHDL代码

轻松:状态图和框图编辑器

HDL伴侣:探索和创建VHDL和Verilog设计

IO Checker:验证FPGA和PCB之间的数百个引脚

5、查看波形并将其导出到:

安捷伦测试设备, 泰克测试设备,

模拟和数字模拟器

6、绘制和分析时序图

DataSheet Pro:专业数据表编辑器

WaveFormer Pro:时序图编辑器和波形转换器

Timing Diagrammer Pro:时序图编辑器

新功能介绍

1、项目级功能

Project Window中的New Port Mappings和Parm Mappings文件夹显示了测试模型如何连接到测试平台。此外,让用户更改映射。

Port Mappings图标颜色指示映射是默认映射(绿色)还是自定义映射(橙色)。在默认映射中,在测试平台中创建的信号与被测模型中端口的确切名称相匹配。当您想要测试诸如两个级联并行加法器电路之类的设计而不首先创建包装两个加法器的模块时,自定义映射会很有用。

2、BuHunter功能

tep Over和Step Into按钮将启动模拟器(如果尚未启动)。

GUI允许您在模拟完成后查询模拟状态,直到您按下红色“结束模拟”按钮。必须先按“结束模拟”按钮,然后才能开始新的模拟。

为GUI添加了模拟调用堆栈显示。这对于调试任务和函数的调用很有用。

3、时序图级别功能

在项目窗口中显示包变量以便于调试。

在“项目”菜单中添加了“导出时序图”,以将项目中列出的所有时序图导出为特定格式。 此功能适用于WaveFormer Pro和DataSheet Pro。 请参见第11.3节“导出一般说明”。

新的命令行选项-M将第二个时序图合并到正在加载的时序图(以前此功能只能从GUI访问,现在可以作为批处理操作执行)。

扩展VCD文件导入兼容性。

功能特色

一、TestBencher Pro

1、VHDL,Verilog和TestBuilder图形测试平台生成

TestBencher Pro是一个图形化的测试平台生成器,可以大大减少创建和维护测试平台所需的时间。对于HDL语言用户来说,最耗时的任务之一是对测试平台进行编码,以验证其设计的运行情况。Janick Bergeron在他的《编写测试平台》一书中估计,有70%的设计时间用于验证HDL代码模型,并且测试平台占产品开发过程中生成的全部HDL代码的80%。

TestBencher Pro使测试台开发中最繁琐的工作自动化,从而使您可以专注于测试台的设计和操作。这是通过以图形方式表示每个总线事务,然后自动为每个事务生成代码来实现的。TestBencher利用所生成语言的强大功能,而工程师不必手动编码每个事务。在进行手工编码时,设计人员将不得不花时间处理设计细节(端口信息,监视系统响应等)以及常见的编程错误(竞赛条件,次要逻辑错误和代码设计问题)。

1、系统级功能

TestBencher可自动执行测试平台开发中最繁琐的方面,使您可以专注于测试平台的设计和操作。这是通过以图形方式表示每个总线事务,然后生成事务代码来完成的。

VHDL,Verilog和SystemC语言生成。

通过图形时序图生成总线功能模型。

支持层次模型。

多组件实例化支持多端口设计。

内置的时序图编辑器,用于创建总线事务。

数据源和目标会自动生成所有文件I / O代码和类定义。

序列识别验证时序序列。

流水线事务可用于实现流水线总线主控器。

基于周期和事件的测试平台。

2、反应式仿真检查

使用“无功测试平台生成”,用户可以选择在MUT输出端口上绘制“预期”波形,并在波形中添加“样本”以测试特定情况。在仿真过程中,样本生成的代码将观察被测模型的输出,并将其与绘制状态进行比较。样本可以执行各种功能,例如暂停模拟以调试问题,报告错误和警告,用户定义的操作以及触发其他样本。

3、反应环有条件地施加刺激

反应式测试基准生成还包括可用于等待被测模型的活动和/或在图的一部分上循环的标记。标记还可以用于从图中调用用户编写的HDL函数和任务。

4、基于时钟和时间的测试平台生成

反应性测试台生成还允许创建“基于时钟的”测试台以及基于激励的生成模型当前支持的“基于时间的”测试台。基于时钟的测试台延迟时钟周期而不是时间,从而允许用户更改其时钟频率而无需更改其时序图。使用高速“基于周期”的模拟器进行测试时,还需要基于时钟的测试台。

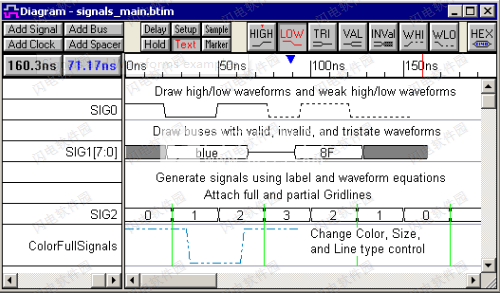

二、WaveFormer Pro

WaveFormer Pro是一种革命性的新型快速原型化EDA工具,可帮助您更快地设计并减少错误。WaveFormer Pro使您能够自动确定关键路径,验证时序裕度,针对重新收敛的扇出效应进行调整以及执行“假设分析”以确定最佳时钟速度。WaveFormer Pro还允许您指定和分析系统时序并执行布尔级仿真,而无需原理图或仿真模型。时序图完成后,您可以为自己喜欢的Verilog,VHDL,SPICE或门级仿真器生成数字激励。WaveFormer Pro还具有导入和注释仿真和逻辑分析仪数据的功能,用于发布质量设计文档。

1、模拟信号

WaveFormer Pro,DataSheetPro,VeriLogger和TestBencher Pro具有内置的交互式HDL模拟器,可大大减少绘制和更新时序图所需的时间。使用以VHDL,Verilog或SynaptiCAD语法编写的布尔逻辑和注册逻辑方程式,您可以根据图中的其他信号来描述信号。您将不再需要手工计算组合电路的输出或计算同步电路的关键路径。SynaptiCAD的交互式模拟器将使用在Logic Wizard对话框中输入的信息生成HDL代码,然后模拟结果。由于模拟器是交互式的,

尽管VeriLogger和TestBencher产品具有内置的Verilog模拟器,但该功能仍包含在其中,因为它使生成测试台架和时序图的速度如此之快,以至于我们无法忍受。在WaveFormer中,它是时序分析和设计功能的基础。交互式模拟器支持多位方程式和真实的最小-最大时序。

2、波形转换功能

WaveFormer Pro和DataSheet Pro支持超过55种不同的格式,用于导入和导出波形数据。从模拟器,逻辑分析仪和时序分析程序导入波形数据。将波形导出到VHDL,Verilog,SPICE,码型发生器,ATE和FPGA工具。这些时序图编辑器还附带了基于PERL的脚本语言,使工程师可以创建自己的导入和导出脚本,以支持定制测试设备和内部开发的软件使用的波形格式。

3、基本时序图编辑功能

绘制和编辑时序图

时序分析功能

模拟波形支持

波形和标签方程

文档功能

批处理模式操作

4、波形比较选项

波形比较是一项可选功能,所有SynaptiCAD时序图编辑器和图形产品均可升级为包含此功能。波形比较功能以图形方式显示两个时序图或单个信号的波形之间的差异。比较两个不同的仿真运行以及将逻辑分析仪数据与仿真运行进行比较时,此功能特别有用。差异显示为比较信号上的红色区域。有容差区域和定时比较的设置,以帮助滤除不重要的差异。

三、Verilogger Pro

Verilog模拟器可提供最佳调试。

准确性和时间至关重要,尤其是在开发仿真和调试方面。我们的Verilog模拟器和编译器将改变您模拟,调试和管理开发过程的方式。

VeriLogger Extreme是高性能的Verilog 2001编译代码模拟器,具有自动测试平台生成功能,可显着减少仿真调试时间。VeriLogger Extreme利用SDF时序信息提供RTL和门级仿真的快速仿真。VeriLogger Extreme支持所有主要ASIC和FPGA供应商的设计库和设计流程,包括Actel / MicroSemi,Altera,Atmel,LSI Logic,QuickLogic和Xilinx。

安装破解教程

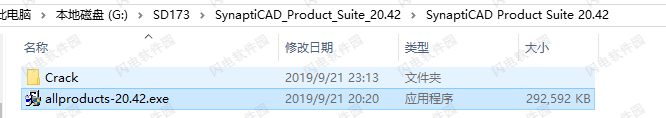

1、在本站下载并解压,如图所示,得到allproducts-20.42.exe安装程序和crack破解文件夹

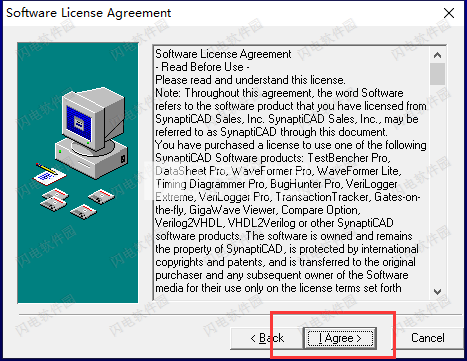

2、双击allproducts-20.42.exe运行,许可协议,点击i a'geee

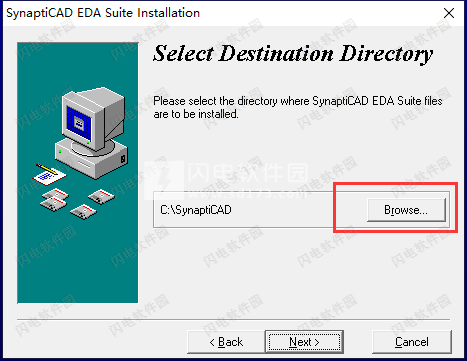

3、选择软件安装路径,点击next

4、安装时间比较久,耐心等待,安装完成,点击finish退出向导

5、将crack中的syncad.lic密钥文件放入安装目录中即可

使用帮助

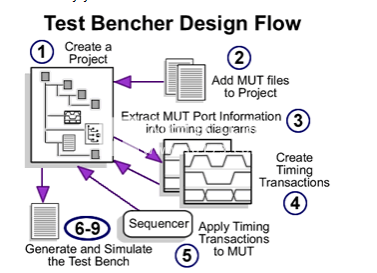

TestBencher Pro设计流程

本章将介绍使用TestBencher Pro生成事务级别模型(TLM)的基本设计流程。 首先,您将创建一个新的项目文件,并添加有关被测模型(MUT)文件的信息。 接下来,您将创建时序图,以生成可重复使用的时序事务。 然后,您将编辑顶级模型,并定义将事务应用于MUT的顺序。 最后,您将模拟测试台。

一、创建一个新项目

项目包含生成TestBencherPro事务级别模型(TLM)所需的所有信息,包括事务图表,顶级文件和代码生成设置。第9章:TestBencher高级项目功能介绍了项目,子项目和创建项目实例。以下是创建基本单级项目的步骤。

创建一个项目:

·选择项目>新建项目菜单选项。这将打开“新建项目向导”对话框。

·“项目名称”既是项目的名称,也是项目的存储目录。

·检查基于事务的测试平台的生成,以使TestBencher生成事务级别的模型,而不是单个图测试平台。

·“语言”下拉列表定义了测试平台模型的生成语言。某些功能(例如有效信号类型)取决于生成的语言,因此此选项会影响TestBencher的操作。

·按“下一步”按钮移至对话框的下一页。

·如果您的项目已计时,请键入时钟信号的名称,以便该项目将为时钟生成一个特殊的事务处理程序。

·按“默认图设置”按钮编辑新图的默认图设置。

·默认情况下,设计的“时钟边缘后默认延迟”设置固定为0的延迟时间。有关如何使用此设置的信息,请参见第9.8节:“图设置”对话框(仅适用于TestBencher)。

·按“完成”按钮关闭“新建项目向导”并创建新项目。

请注意,TestBencher会自动打开“项目”窗口,并使用顶级模板文件和模板图填充它。模板图是您添加到项目中的任何新事务的起点。“项目”窗口将是您浏览事务级别模型的不同部分的主要资源。

“项目”窗口的基本控件:

·右键单击“项目”树中的任何节点,以打开一个上下文相关的弹出菜单,其中包含可以对该特定节点类型执行的所有操作。

·在任何节点上单击鼠标左键以对该节点执行默认操作(通常在适当的编辑器中打开该文件或对象)。

·要展开或隐藏树的分支,请单击expandNode或collapseNode。

·拖放列标题以调整列大小。

“项目”窗口的“基本文件夹”:

每个项目中都会创建几个文件夹,这些文件夹用于组织测试平台不同级别的文件和对象。这些文件夹中的每一个将在手册的不同地方进行讨论。作为概述:

·“模拟模型”文件夹包含完整的编译设计,“激励和结果”图以及来自模拟器的日志文件。有关更多信息,请参见第8章:生成和仿真。该区域用于分析和调试已编译的仿真。

·被测模型包含带有端口的模型,这些端口将连接到测试台。默认情况下,当按下“提取MUT端口”按钮时,未实例化在另一个模型中的第一个模型被选择为测试中的模型。第一次构建后,您可以选择右键单击其他模块,然后选择“设置为测试中的模型”以控制在测试平台中实例化的模型。有关更多信息,请参见步骤3:将端口提取到模板图中。

§端口映射和参数映射显示了如何连接模型。默认情况下,具有相同名称的信号会映射在一起。您可以通过以下方式自定义映射

·事务级别模型是测试平台的顶级模板文件。该文件夹包含所有项目级别的类,变量,类方法和子项目的实例。有关更多信息,请参见第7章:事务级模型事务定序器。

·“TransactionDiagrams”文件夹包含模板时序图,已添加到项目中的时序图以及相关的生成的源代码文件(在时序图下方的级别)。主图带有波形图标,而从属图带有回送图标。有关更多信息,请参见第2章:时序交易器基础。

·TestVectorFiles文件夹包含输入和输出测试矢量文件。第8章:类和变量,以获取更多信息。

·“项目库”文件夹包含可在当前项目中实例化的所有子项目。第9.1节:子项目讨论了该文件夹。

·“用户源文件”文件夹包含要在测试平台中使用的源文件。带有绿色复选标记图标的文件已被编译到测试台中。带有红色X图标的文件尚未被编译步骤3:将MUT端口提取到模板图中具有更多信息。

二、将MUT添加到项目

设计的被测模型(MUT)文件应添加到项目中。TestBencher将使用这些文件将MUT实例化到您的测试台中,并提取信号和端口信息,以用于激发MUT的事务图中。

将MUT源文件复制或添加到项目中:

·右键单击“用户源文件”文件夹,然后将设计文件添加或复制到项目中。

·“复制”菜单将源文件复制到项目文件夹,并将副本添加到项目列表。添加功能添加文件及其路径而不进行复制。也可以通过从主栏中选择“项目”>“添加用户源文件”菜单来添加文件。

·如果您的MUT需要从编译到其他库中的包中定义,请按照第8.5节:将包文件解析为库中的步骤进行操作,以确保正确解析了这些包。如果您的MUT解析确实需要将文件编译到多个库中,则可能需要在第一次解析后直接设置所需的测试模型,然后再次解析(请参阅步骤3:将端口提取到模板中)。

(可选)实例化项目中的多个MUT

如果您的项目仅挂接一个源模型中的顶级模型,即被测模型,则可以跳过此过程并继续执行步骤3。但是,此产品支持多个MUT和同一MUT的多个实例化。。首先构建项目,然后选择您的MUT并根据需要编辑新MUT的端口映射。这应该在创建事务之前完成,以便在事务构建步骤中可以使用所有信号。

·按“构建”按钮分析源文件,并使用模块信息填充项目窗口树。

·深入到“用户源文件”节点,然后在MUT上单击鼠标右键以打开上下文菜单。

·选择“设置为测试中的模型”。

·请注意,该模块已添加到“待测模型”树节点中。绿色表示端口映射正在使用与MUT的端口名称匹配的默认值。

·从右键单击上下文菜单(如上所示)中选择“测试中的克隆模型”,以创建MUT的另一个实例。

·程序通过匹配相同的名称信号来猜测端口映射。但是,从右键单击上下文菜单(如上所示)中选择“编辑被测模型”,将打开一个对话框,该对话框允许更改模型实例名称以及端口和参数映射。

·双击端口名称将打开一个下拉列表,您可以在其中选择其他端口或键入其他名称。

·在编辑完实例映射后,树中的图标将变为红色,表示如果项目中发生其他更改,程序将不会覆盖端口。

·如果要研究模型实例并定义创建的任何新信号,请按MakeTB按钮,然后双击“Transaction-LevelModel”节点以打开带有生成的测试基准代码的编辑器。

·确保在代码生成模块之外定义新信号。并将它们添加到$InstantiateMUT代码生成块之前的某个位置。

VHDL和Verilog混合设计:

如果您使用的是多语言设计,或者您更习惯使用特定的HDL语言,则生成的测试平台和设计模型不必使用相同的语言。您将需要使用测试平台生成语言编写包装模块,以其他语言实例化模型。您还将需要多语言模拟器来编译和调试设计。

·在步骤1中,创建项目时,将语言设置为将生成测试平台的语言。还将模拟器设置为多语言模拟器的名称。

·使用测试平台语言创建一个包含包装模块的新文件,该文件可实例化设计模型并在两种不同语言之间映射信号类型。设计模块实例化的语法将由您的模拟器指定。包装器的端口将是测试台驱动和观察的信号。

·如上所述,将设计文件添加到“用户源文件”文件夹中。TestBencher可以解析VHDL和Verilog文件,也可以将文件发送到多语言模拟器。

三、将端口提取到模板图中

当TestBencher创建项目时,它还会生成一个模板图。新的事务图将包含与模板图相同的信号,波形,参数和属性。在创建定时事务之前,先设置模板图是一个好主意,这样所有定时事务都将具有相同的接口信号。

打开模板图:

·在“项目”窗口中的“模板图”文件夹下,双击名为projectname_templateDiagram.btim的图以打开模板图窗口。

·如果在项目创建步骤中创建了默认时钟,则模板图将包含该时钟作为输入信号,并且还将存在一个时钟生成器图,其中将该时钟作为输出。时钟应仅由一个定时事务驱动,以便可以在模拟结束时适当地中止时钟。

将MUT的端口提取到模板图中:

·单击“从MUT提取端口”按钮以构建MUT,并将MUT端口的信号插入模板图中。

·蓝色图标指示信号的方向。用鼠标悬停在方向图标上,工具提示会告诉您每个图像的含义。

·默认情况下,TestBencher从顶级模型中提取端口(未在其他模型中实例化的端口)。

·首次构建后,可以选择右键单击其他模块,然后选择“设置为测试中的模型”以控制在测试台中实例化哪些模型。

·请注意,用户源文件带有绿色的复选标记,表示它们已构建。

·双击任何组件将打开一个滚动到代码中该位置的编辑器。

·添加要在所有测试台事务中显示的其他图形对象,结束图标记和变量。

·选择“文件”>“保存时序图”以保存模板图。

四、创建定时交易器图

TestBencher为项目中的每个时序图生成一个事务处理程序,该事务处理程序代表您正在创建的总线功能模型的可重用接口规范(例如,读取周期,写入周期,中断周期)。这些事务处理程序是Verilog的模块,VHDL的实体/体系结构对和TestBuilder的类。不管使用哪种语言,事务处理程序都使用相同的通用体系结构。并且在所有语言中,事务处理程序都具有类似的功能性API,可用于触发它们(图表应用调用)。教程和第2-6章介绍了如何绘制时序图和控制生成的代码。创建新的时序图时,它将包含模板图的所有信号和属性。对要在测试台中调用的每个定时交易器执行以下步骤:

创建一个新的定时事务处理程序:

·在“项目”窗口中,右键单击“事务图”文件夹,然后选择“创建新...事务处理器”菜单之一。这将打开一个文件对话框,用于创建和保存该图。

·保存图表后,将其添加到“事务图表”文件夹中。该图将包含模板信号和属性。

主事务器是运行一次然后停止的事务,由波形图标表示。

从属事务器是将连续循环直到收到中止调用的事务,并通过带有波形和环回线的图标显示。从事务通常在测试平台的开始处开始,一直运行到测试平台完成为止。

·使用时序图编辑器通过绘制波形来创建时序图。可选对象(例如样本,标记,延迟,变量和类方法)将在本手册的后面部分进行详细讨论,并在教程中进行演示。有关如何创建事务的信息,请参见第2-6章。

·选择文件>保存时序图菜单选项以保存时序图并生成HDL代码。每次保存时序图时,都会为其生成新代码。

切换到从站和主站:

时序图的“从机”和“主机”设置会影响为时序事务生成代码的方式。创建时序图后,您可以通过执行以下操作更改为其他设置:

·在“项目”窗口中右键单击时序图名称,然后从上下文菜单中选择“图设置”以打开“图设置”对话框。

·然后检查“从属事务处理”或“主事务处理”单选按钮。

查看生成的HDL源代码:

由于每次保存时都会重新生成时序图的源代码,因此您不应对代码进行任何手动更改。但是,有时有时可以根据图中的结构来了解底层代码的变化方式。

·单击“源代码”按钮以打开编辑器并查看代码。

SynaptiCAD软件套件 SynaptiCAD Product Suite 20.51破解版 含教程

SynaptiCAD软件套件 SynaptiCAD Product Suite 20.51破解版 含教程

SynaptiCAD软件套件 SynaptiCAD Product Suite 20.51破解版 含教程

SynaptiCAD软件套件 SynaptiCAD Product Suite 20.51破解版 含教程