Expedition Enterprise破解版是超强的企业级PCB设计仿真平台,具有强力的性能和友好的环境,涵盖PCB设计的方方面面,具有创新设计流程,图形用户界面,不管是进行原理图设计、约束定义、PCB布局以及库创建和管理等等都为您带来强大的支持!Xpedition Enterprise流程提供了从概念到制造交接的干净,集成的设计系统。 从系统定义和仿真到原理图输入,约束定义,布局,验证,可制造性设计,设计数据打包(从移交到PCB制造)的各个方面均可使用工具。真正的可完全控制的设计过程,从简单到复杂的电子系统统统能够轻松搞定,结合其专利的技术,在提高质量的同时减少时间投入,减少与零件研究和库创建等相关的成本和时间,面对日益增长的业务压力和内部挑战,电子产品开发充满风险。但是,如果某些最佳实践包括完全集成和优化的多域解决方案(支持机械,电子,电气和软件),则可以降低这些风险。

Xpedition VX.2.7新功能

一、布局

1、JT支持

JT(木星分割)是一种ISO标准化的3D数据格式,用于产品可视化,协作和CAD数据交换。JT模型重量轻且结构合理,因此可以快速快速地实时加载,着色和操纵大量组件。在此视频中,我们将演示直接从XpeditionLayout生成JT的过程。

2、安置大纲交换

为了在2D和3D域中正确传输设计意图,现在可以传输由NX驱动的2D数据。在此示例中,我们将机械外壳标记为机械单元,并传播组件接触电路板表面的位置的放置轮廓。

3、锁定状态

在大多数情况下,组件归一个域所有,不应被另一个域修改。为防止这些关键组件意外移动,您可以锁定该组件,该组件将自动发送到另一个域。

4、通知和监控更新

为了提醒设计者,协作文件夹Xpedition中有未处理的文件待处理,而NX有几种方法可以监视和通知设计者未处理的文件。在本视频中,我们将介绍这些通知的几个示例。

5、添加部分选定的迹线

此新命令将允许选择完整的轨迹集,并在重新布线时保持扇出状态不变以供重复使用。

6、将图钉添加到草图计划

现在可以通过选择引脚来选择分配给草图路径或草图的连接。

7、复杂通孔的更换和管理

按名称用不同的复杂通孔替换现有的复杂通孔。

8、射频对复杂通孔的支持

曲折编辑现在支持复杂通孔中的连接点,以与其他路由命令获得一致的用户体验。

9、改进的选择和突出显示

现在,您可以看到显示为选择或突出显示图案一部分的图层颜色。它还允许按网或类进行颜色图案。

10、Fablink中的板对板

可以将选择原点分配给Fablink中的板对象。这样可以在移动对象时更好地进行控制。

11、通过网络过滤危害

这是一个新选项,允许用户过滤危害显示并仅对过滤后的网进行危害更新。

12、手动将锯齿调添加到差分对

锯齿命令已添加到上下文相关的RMB命令菜单中,以与差异对一起使用。这也提供了可以手动修改的调谐盒。

13、放置测试点

这是用于手动放置测试点的新方法。它突出显示需要测试点的网络,并在满足测试点要求时清除它们。

14、放置多个零件

手动一个接一个地放置零件,或自动排列。

15、路由阻塞(允许一网)

此功能允许单个网络忽略路由障碍。将网络分配给路线障碍物的属性。

16、布线时交换引脚

这是布线网络时的一个新选项,可以进行引脚交换。这适用于单网和差异对。

二、多板系统设计

优化的同步和DRC

现在可以通过一次检入系统设计来完成将多个PCB与系统设计相关联的操作。还优化了用于管理每个板的同步状态的算法,以显着减少分析设计同步的时间。对于大型系统,此新过程可能会花费几分钟的时间来检查每个电路板。此外,已经创建了新的DRC来验证配对的连接器。这样可确保原理图上的配合与库中的配合相匹配。

三、原理图捕获

1、用户界面和可用性改进

此版本包含多个可用性改进。网格选项,制表符关闭和键盘快捷键得到增强,并变得更加简单。

2、在设计中识别PartQuest零件

对Partlister定义文件的新添加将创建一个报告,该报告显示已使用PartQuest创建设计中的哪些零件。

3、DRC验证中的原理图引脚类型

设计人员现在验证分析原理图级别(和模块级别)的引脚类型,而不是仅分析符号引脚类型。优先顺序为:实例>块>符号。该工具还支持I / O优化器的引脚类型替代。这使您可以直接从原理图中利用任何引脚类型的更改。

四、数据管理

1、与活动工作区集成的EDM元数据

新功能将带有设计指标和基准历史记录的EDM元数据嵌入到Teamcenter Active Workspace客户端中。

与EDM集成的Teamcenter Active Workspace

EDM中的新功能提供对Teamcenter Active Workspace客户端的直接访问,并提供了与Teamcenter相关联的功能。

2、EDM合作计划

EDM Collaborate中对过滤方案和方案管理进行了改进。用户现在可以为基线和发布的数据创建过滤方案。还采用了用于过滤方案,PCB视图方案,示意图视图方案和数据视图方案的通用方案管理系统。

3、EDM Server管理改进

EDM管理方面的改进使监视和维护EDM服务器的运行状况变得更加容易。新功能包括自动EDM协作缓存清除,自动日志文件清除,日志文件改进和Data Analyzer改进。

4、组件的平铺视图

EDM Collaborate 2.7现在提供了切片视图,以利用查看3D模型图片或EDM库中定义的默认组件图片的优势。用户可以选择旁边的图块图标,以在显示列和图块之间切换。

5、设计变体比较

EDM Collaborate查看器改进了设计变体的比较。在变体管理器中定义变体后,EDM Collaborate Viewer允许用户比较相同设计版本或不同设计版本的不同变体,甚至不同设计之间的变体。随着设计随着时间的推移进行修改,这使用户可以跟踪变量的变化。

6、从EDM Collaborate拖放到原理图

EDM提供了使用拖放简单性将库零件从EDM Collaborate实例化到Xpedition Designer的功能。从详细的零件视图中,用户可以从主磁贴中选择默认的库视图,或显式定义要用于放置的符号。

7、协作笔记通知

可以创建,发布协作笔记,并将其传达给分配给该笔记的所有用户。

8、恢复以前删除的文件

EDM Design支持垃圾桶概念,该概念将保留已删除的信息,从而使管理员可以还原以前删除的文件,文件夹或整个项目。在EDM Server上启用后,所有删除的项目都将保留在垃圾箱中,从而使管理员可以进行排序,搜索,还原或删除。有关对象删除和恢复的所有历史信息都存储在EDM中,并且可以使用show history命令获得。

9、EDM导入多个零件

一次将多个零件导入EDM。该示例导入了电阻,电容器和集成电路的PartQuest下载。在EDM库主控室中使用EDX导入来快速导入组件,检查导入,并注意参数和图形信息已加载。有了这些预加载的内容,您现在就可以将数据修改为库规范并发布给用户。您还可以使用此功能,简单,准确,快速地将零件从一个库移动到另一个库。

10、自定义组件图像

EDM Library支持可在EDM Library座舱中或EDM Collaborate Web界面中显示的自定义组件图像。用户可以添加一个或多个组件图像并将一个定义为要在Web上显示的默认图像。在Web上查看这些组件时,这些自定义图像将显示在详细的组件窗口中以及组件搜索图块视图中。

11、PartQuest拖放

通过将PartQuest中的选定零件直接拖放到Xpedition Designer中的项目中的新功能,简化了零件的获取。零件信息包含用于完整PCB解决方案的参数数据,原理图符号,布局封装,甚至3D模型。

12、利用EDM对Hyperlynx进行集成改进

从EDM启动HyperLynx,并根据用户管理模拟“沙箱”中的数据。如果从Xpedition创作工具中启动HyperLynx,也会跟踪结果。

四、设计验证

1、利用EDM对Hyperlynx进行集成改进

从EDM启动HyperLynx,并根据用户管理模拟“沙箱”中的数据。如果从Xpedition创作工具中启动HyperLynx,也会跟踪结果。

2、启用HyperLynx和Xpedition的不同步版本

HyperLynx版本与Xpedition的前两个版本不同步。这样可以更频繁地更新分析工具,同时保持更长的稳定创作流。

3、自动建模FPGA以进行原理图分析

现在可以使用原理图分析自动对定制FPGA器件建模。可免费下载Altera和Xilinx组件的在线数据库。这极大地减少了对大型定制组件进行建模所需的时间。

4、链接并查看数据表以进行示意图分析

现在,您可以直接从原理图分析项目中打开数据表。数据表的位置可以直接在材料明细表上(或在Designer的属性中)指定。快速找到要检查的数据表,可简化结果分析。

5、更新BOM进行示意图分析

新功能使您可以维护与具有不同零件号的零件的模型分配连接,以进行示意图分析。

功能特色

一、系统设计-从概念到制造

Xpedition®Enterprise流程提供了从概念到制造交接的干净,集成的设计系统。 从系统定义和仿真到原理图输入,约束定义,布局,验证,可制造性设计,设计数据打包(从移交到PCB制造)的各个方面均可使用工具。

1、紧密集成的流程

Xpedition紧密集成的设计环境,加上其行业独有的技术以及能够满足中型到大型电子公司需求的能力,确实使其在竞争中脱颖而出。它具有通用的数据库和用户界面,其规则消除了管理多个工具以完成设计的负担。

电气和制造约束管理系统,连同其设计数据和库管理,为本地或全球分散的设计团队提供了支持,以利用他们的资源并缩短设计周期。从概念到制造,始终保持数据完整性。

Xpedition与库和数据管理系统以及约束管理器集成在一起,为组件库,设计数据版本控制和管理,设计重用,高速和制造规则的输入和管理以及与公司PLM系统的集成提供了中央基础架构。

设计完成后,与制造输出工具的集成可确保维持设计的完整性。

2、行业独特的技术

虽然紧密的集成提供了一个无缝的环境来支持PCB系统设计团队,但Xpedition已经超越了PCB设计解决方案的传统定义,并且包含了许多行业独有的技术。

这些技术满足了电子公司最先进的业务需求,使开发团队能够以更低的成本将更具竞争力的产品更快地推向市场。

这些独特的技术分为三类:并发(并行与串行)产品开发过程;使用和分析最先进的IC和PCB制造技术;以及PCB设计师与产品开发过程中的其他学科之间的协作。

二、系统定义

1、设计输入

Xpedition为设计创建,定义和重用提供了完整的解决方案。它提供了电路设计和仿真,组件选择和库管理,信号完整性计划,项目管理以及基于团队的设计所需的一切。使用原理图设计器,多个工程师可以同时进行同一个设计,而无需进行经典的拆分和重新合并过程。一位工程师所做的更改将立即反映在主数据库中,团队可以查看这些主数据库,从而使原理图图纸之间的界面保持同步。除了经典的原理图符号,用户还可以使用电子表格输入组件和互连数据。这对于容纳极高引脚数的封装特别重要,在该封装中,原理图符号将占据数页。

原理图设计器还与产品生命周期管理系统集成在一起,从而在整个公司范围内提供设计数据,PDF原理图和BOM。它还具有基于Internet的集中式库,因此仅需要维护公司库的一个版本。

2、FPGA-PCB设计协作

为了满足不断增长的FPGA和PCB设计需求,FPGA I / O优化器是一种快速有效的解决方案,用于在PCB布局中分配FPGA I / O至设备的引脚。集成了FPGA和PCB设计流程,以提供自上而下的FPGA封装和PCB并行设计,从而缩短了设计周期,并优化了系统级性能。

通过维护主要FPGA供应商的零件库,优化器可提供有关所选器件每个引脚的所有重要信息。然后,用户选择将所有信号签名,或者仅将那些被认为对PCB设计至关重要的信号签名。他们还可以为关键信号分配I / O标准。这样,可以在PCB布局之前优化单个或多个FPGA的引脚排列,以确保最佳的系统性能,从而减少PCB布线拥塞和设计周期时间。是否需要交换PCB上的引脚以进一步改善布局? FPGA优化器知道哪些引脚可互换,哪些引脚不可互换。它还通过充当数据管理工具,监视每个流程并管理发生的任何变化来保持FPGA和PCB流程之间的一致性。

优化器接收PCB上进行的引脚交换,并更新必要的FPGA文件。

然后,它基于HDL设计和引脚I / O分配过程生成FPGA布局和布线约束,并基于“后布线”引脚数据创建必要的符号,原理图和层次结构关联。

3、约束定义

Xpedition理解并遵循大量的高速和制造约束条件(规则),这些约束条件是通过工程师直接输入或通过布局前高速分析的接口来设置的,在整个布局和验证步骤中都应遵守,以确保设计正确结果。

约束管理器提供了一种完全集成的,约束驱动的设计方法,可通过自动化设计规则通信并消除不必要的PCB原型和重新设计来降低设计成本和缩短产品上市时间。并且,与原理图设计人员一样,多个工程师可以同时输入和编辑约束,而无需使用容易出错且耗时的划分和重新加入方法。

团队可以实时查看编辑内容。约束管理器为制造以及电子和物理高速规则提供公共约束输入。约束管理器具有一个易于使用的类似于电子表格的GUI,该GUI由设计数据库引导,并与原理图和布局进行交叉探测。

■规则保留在网络重命名,连接性增加/删除,引脚和/或门交换以及堆叠更改上。

■GUI提供了轻松的差分对创建,并行规则输入和引脚对创建。■分层约束输入可实现简单分配 具有过滤和排序功能的复杂拓扑。

三、PCB布局

Xpedition是业界最强大的物理布局解决方案。 通过将易用性与高级功能相结合,Xpedition为设计师提供了领先的技术来创建当今最复杂的设计。 它包括交互式和可定制的多通道自动路由控件,以应对设计挑战,例如差分对路由,网络调整,制造优化以及HDI /微孔和堆积技术

1、PCB设计中的物理布局技术领导者

Xpedition的布局和布线技术代表了PCB设计的革命性进步。 业界领先的自动路由技术的强大功能与交互式编辑功能相结合,可产生一个单一,强大且易于使用的设计环境。 这种环境消除了为完成工作以及管理自动布线器和交互式编辑上的约束之间的差异而跳来跳去之间的负担。

Xpedition提供了前所未有的控制,可根据需要在自动和手动编辑之间轻松切换。 从简单的任务(如定义电路板区域)到涉及维持高速信号条件的复杂程序,系统和设计人员实时协作即可实现所有目标。 Xpedition技术的最终结果是缩短了设计时间,提高了生产率并提供了无与伦比的设计质量

自动和交互式路线选择

■单个集成的布局和路线编辑环境,减少了总设计时间并提高了生产率。■保留了所有物理规则和高速规则。 ■消除了建立时间。■基于形状的,真正的45°布线和先进的任意角度推/推功能,可应对最具挑战性的BGA模式。■有史以来最先进的自动布线技术。 随时停止和启动自动布线器:所有结果都将根据构造正确。■通过减少线段,防止锐角和应用焊盘进入规则来动态清理走线。

动态区域填充

在编辑电路板时,Xpedition会自动清除走线,过孔和焊盘周围的填充区域。

动态区域填充是如此之快,它允许用户在进行所有必要的编辑时保持其区域填充处于打开状态。 移动通孔可以推和推其他通孔,走线和区域填充,并自动保持连接。

区域规则

“按区域划分规则”功能极大地改善了BGA和其他细间距零件的布线。 规则区域代表在线和批处理DRC以及交互式和自动路由中遵循的完整规则集。 规则区域可以按图层定义,也可以通过Xpedition的布局工具轻松路由和编辑差分对,从而轻松快捷地完成操作,这将改变您对高速设计的看法。

5分配给任何多边形,矩形或圆形。 在规则区域中使用时,迹线的宽度和间隙会自动更改。

设计人员还可以更改规则区域中的尺寸和跨度,以最大程度地完成路线。

具有可变通孔图案的多犁

Xpedition的多重犁功能使设计人员能够同时对多个网络(包括差分对)进行布线,并具有任意角度的真正45°布线以及偏置角度布线。 它甚至可以处理交错引脚区域中的布线。 布线的走线推动并推动其他过孔和走线,并根据需要自动清除区域填充。 只需触摸一下按钮,就可以轻松地对各种可选的通孔样式进行更改,从而增强了灵活性,可以路由到设计的密集区域。

2、高速布局

设计人员必须越来越多地管理信号质量,以实现系统性能并减少原型迭代次数。 Xpedition的高速设计是设计环境中不可或缺的一部分。 高速规则的动态DRC,针对最复杂的高速约束定义的自动调整,以及动态调整可使网络保持调整。 其垫片技术有助于管理串扰。

网络调整

在交互式路由时,将显示图形调整辅助以进行指导。在编辑过程中修改不正常的网络会自动重新调整。当用户编辑网络时,“危害”对话框会动态更新,以提供对其约束的即时反馈。网络也可以在自动路由过程中自动调整。设计完成后,将自动维护已调整的网络。

差分对路由

使用Xpedition路由和编辑差分对可以轻松快捷地完成,从而改变了高速设计的视野。阻抗可以通过层轻松控制,并且可以通过层和网络类别建立对间距规则。如果编辑了一条迹线,该对中的另一条迹线将自动随之移动。相邻层差分对路由功能为在密集PCB上路由关键信号添加了另一种有价值的选择。

动态危害评估

设计危害可以动态显示,并且可以单独选择和着色以方便识别。修复危害后,会将其动态从危害列表中删除。

3、同时设计

利用一项革命性的,专利的和令人兴奋的技术,该技术使遍布本地或全球的多个PCB设计人员可以通过LAN或WAN同时处理单个设计数据库,从而提供了空前的设计效率。与采用拆分联接方法进行设计协作的传统团队设计方法不同,并发团队设计不需要物理分区,并且每个设计师都可以实时查看所有其他客户编辑。由于不需要进一步的培训或复杂的设置,因此可以随时随地邀请设计人员参与对时间要求严格的项目的协作,从而大大缩短了设计时间。非常适合大型,复杂的设计或专业人士在混合信号环境中工作时的理想选择。

4、多用户自动路由

允许多个设计人员在同一数据库上同时进行设计的相同技术可以实现多处理器自动路由。通过在LAN或WAN网络上的多达15个处理器客户端上执行自动路由,用户可以将使用时间提高多达10倍。对于超大型,高度受限的电路板,这可以将时间从几天缩短到几小时。结果不仅减少了设计时间,而且使您有机会运行多种布置和约束方案并选择最具成本效益的方案。

5、总线路由

自动布线很少用于密集的,高度总线结构的PCB,因为手工布线会产生并行的团队设计技术,使设计人员可以在同一PCB上同时工作,从而加快了设计过程。

6denser,更具制造性和美学效果。但是,手动路由非常耗时且乏味。

熟练的设计者或工程师确定公共汽车及其分配飞机的拓扑结构,以满足高速约束。

Xpedition拥有独特的技术,将设计师和工程师的技能与自动布线的速度相结合,消除了乏味,而专注于产生更好的设计。

拓扑计划程序提供了一种交互式方法,用于定义总线的拓扑结构,将其分配给平面并指定许多专门的规则。该计划与设计数据一起保存,可以修改。然后可以按照计划执行拓扑路由器以自动路由互连,从而消除了乏味的跟踪数字化。结果模仿了熟练的设计人员,但大大缩短了设计周期并提高了生产率。

6、嵌入式无源设计

随着IC和FPGA速度和密度的提高,它们需要更多的无源组件(电阻和电容器),有些可能需要数百个。

与嵌入式SMD相比,将它们实现为嵌入式组件可以显着减小电路板尺寸并提高性能。

Xpedition提供了一个完整的解决方案:权衡工具根据电路板的尺寸和成本,被动材料的选择,材料供应商的库驱动的自动综合以及完整的制造数据生成,来决定在嵌入式还是离散中实现哪些组件。

结果是自动化的任务可能需要数周的人工。

7、高级互连路由

如今,随着BGA,CSP,COB和DCA封装增加了电路板密度,高级互连面临的挑战和解决方案十分普遍。这些电路板设计中使用的积层和微孔结构进一步使布线复杂化。

Xpedition为高级互连设计提供了领先的技术。 Breakout and Escape技术可通过极细的间距引脚/球快速布线最高引脚数的封装。可以定义堆叠和交错的通孔定义,从而可以控制放置的通孔结构。

超越传统的层压材料层配对,可简化层压材料上堆积结构的设计,从而能够实现高密度,高引脚数器件的逃逸图案。堆积区域的间隙通常比其下面的层压板小。

可以建立每个通孔跨度的延迟值和间隙来解决这些问题。此外,Xpedition具有真正的45度布线和先进的任意角度推/推功能,可应对最具挑战性的BGA模式。

8、高密度BGA扇出

对于设计师而言,连接到当今的高级软件包可能是一项耗时的任务。 Xpedition中行业独有的技术可实现高引脚数和密度BGA的自动扇出。

遵循Mentor发布的设计指南,用户可以使用HDI / microvia层定义扇出图案,并在几秒钟内开发出图案。然后,在其他PCB组件的上下文中,定义并自动产生一个与PCB其余部分连接的分支。将过去需要数天的设计时间减少到几分钟。

9、射频电路设计

随着无线技术的发展,更多的PCB设计将RF电路与模拟和数字互连结合在一起。通常,设计这些板需要两个完全不同的工具和库。 Mentor的领先技术可实现Xpedition环境中的RF电路设计,包括原理图输入,使用与RF仿真提供者相同的库来合成RF零件,操纵和编辑RF电路以及与安捷伦和AWR等供应商的RF仿真器直接接口。结果是一个高效率的过程,该过程整合了设计和设计团队,消除了库的重复和同步,并利用了Mentor的PCB设计和RF模拟器供应商的技术优势。

四、分析与验证

1、信号完整性,时序分析和EMI

借助Xpedition流程,可以在整个设计过程中(而不是最终)解决和纠正信号完整性和电磁干扰(EMI)问题。 在约束的驱使下,这可确保设计首次正确,从而有效地减少了设计迭代,并促进了最佳系统性能。

HyperLynx®为传统的高速互连,新兴的SERDES和DDR2 / 3技术以及高级SERDES和DDRx协议提供布局前和布局后信号完整性,串扰和EMC分析。

HyperLynx易于学习的分析环境使其成为Xpedition的每个桌面标准。

更高频率的设计和政府法规越来越重视EMI控制。 这通常需要一个原型板,在一个屏蔽室中进行测试并重新设计。

2、电源完整性

利用当今的低电压和多电压IC,电源和地线不再易于设计和分析。 PCB可以包含多达30个通过夹具锯切到PCB层中的配电网络。必须分析这些网络的直流电压降(向所有IC引脚提供足够的功率),电流密度(通过网络狭窄部分的电流过多)和交流电(干净的电源)。 HyperLynx PI(电源完整性)为工程师和设计人员提供了复杂配电网络的布局前和布局后分析,以确保PCB的正常运行和高可靠性。

3、热分析

随着产品变得越来越快和越来越小,热管理问题越来越多。 HyperLynx Thermal,FloTHERM®和FloEFD®为PCB以及整个产品中的PCB提供了热分析功能(外壳,风扇,散热器等).PCB设计人员可以使用这些功能进行分析在PCB上确定组件的良好位置。外壳的机械设计人员可以将PCB插入完整的产品中,并对其进行分析,以查看热量是否能够正确散发。结果是设计具有更高的可靠性,并且可以在没有多个原型或重新旋转的情况下进行制造。

4、混合信号验证

HyperLynx Analog™在系统或板级验证模拟和混合模拟/数字设计。它紧密集成到原理图设计器中,并结合了易用性和强大的仿真,激励准备以及复杂的电路分析和验证。

ModelSim®是世界上最流行,使用最广泛的VHDL和混合VHDL / Verilog模拟器,也是发展最快的Verilog模拟器。 ModelSim产品具有独特性,它使用了诸如Optimized Direct Compile(优化的直接编译)技术来加快编译时间和仿真性能,Single Kernel Simulation(SKS)和Tcl / Tk来提高开放性和调试速度。这些独特的ModelSim创新带来了领先的编译器/仿真器性能,完全自由地混合VHDL和Verilog以及无与伦比的定制功能。

5、设计规则检查

HyperLynx DRC是完全可自定义的规则检查工具。 它验证了不容易模拟的复杂设计规则,例如EMI / EMC规则。 借助19条标准设计规则检查项目,例如走线是否穿过裂痕,参考平面变化,屏蔽以及通过检查,您可以快速,轻松地确定电路板上的故障点,这些故障点可能导致EMI / EMC,信号完整性和电源问题 诚信。

HyperLynx DRC通过自动化对象模型(AOM)访问数据库对象,并允许对这些对象进行高级几何操作。 这使您可以唯一访问设计数据库,并允许开发多种类型的DRC。 借助对VBScript和JavaScript的支持以及AOM和DRC编码标准的详尽文档,以及内置的脚本调试环境,用户可以立即编写自己的DRC。

五、多学科协作

开发电子产品不仅需要PCB设计。机械外壳必须经过设计。

在整个设计过程中必须涉及采购,测试和制造,以确保产品能够及时达到批量生产,从而进入市场。 Xpedition为这些学科提供了在产品开发过程中进行协作的能力。

1、ECAD-MCAD协作

过去,电气设计人员与机械设计人员之间的通信是通过纸质或大量数据传输进行的。 Xpedition为PCB设计人员提供了3D查看功能,可将PCB插入外壳并识别重大错误,例如组件对外壳的干扰。

但是真正的协作不只是3D观看。 Xpedition还提供了用于增量更改提案的双向电子通信的功能。使用此ECAD-MCAD合作,任一学科都可以提出其领域的变更建议,并将该建议传达给另一方。然后可以对提案进行分析,拒绝,接受或提出反对。这个数字过程一直持续到两个学科都满足为止,此时更改反映在两个数据库中。

2、PCB设计师–供应链合作

PCB设计的最新变更可能会对采购,制造和测试交付批量生产目标的能力产生负面影响。 Xpedition使PCB设计人员可以提出更改建议,并将该建议以电子方式传达给其他供应链组织。设计审查工具使这些组织可以查看建议的更改,并通过标记和红线与设计者沟通,以确认是否可以接受此更改。此协商过程将继续进行,直到达成可接受的解决方案为止。

六、DFM验证

制造数据的创建以及到生产现场的分配在设计过程中的某个时刻提出了挑战,因为从时间和金钱上来说,错误可能变得非常昂贵。

约束管理器包含在设计过程中经过动态检查的制造规则。此外,Xpedition与Valor NPI紧密集成,可利用制造方面最终验证所使用的相同约束,来访问业界领先的DFM验证解决方案。

可以在布局环境中直接创建制造文档和输出,因此任何最新的布局更改都将自动同步。自动化和可自定义的制造数据创建和分发可提高质量,准确性和设计吞吐量。

数据可以ODB ++格式输出,以确保包括并同步所有制造数据。

还支持其他CAM格式,包括Gerber,ATE和AIS Drill

1、DFM验证

与Valor NPI产品同时进行DFM验证是将可制造性纳入PCB设计过程的最有效方法。确定设计期间进行制造,组装和测试改进的机会,并避免制造引起的工程变更。您甚至可以自动执行DFM验证的时间间隔并及时查看结果,从而简化设计流程并提高效率。如果发现错误,只需单击一下即可将您带到PCB设计上的位置,以便您解决问题。

综合分析

您的DFM流程仅与您使用的验证工具一样好。

当今,小型化的高层设计无法通过手动方式可靠地进行审查。 DFM验证软件可以通过以下多种方式来分析您的PCB设计:■275个结构检查■250个装配检查■100个高级基板检查■40个微孔检查■30个面板检查此外,DFM验证工具还可以根据设计检查您的网表数据,以确保在此关键步骤中没有致命错误。它会验证您的BOM是否与设计匹配,以及您的“批准的供应商列表”(AVL)中的所有组件是否都可以接受。

设计中心定制

在可制造性方面,每个设计中心和每种技术类型都有其独特的要求。

从数据归因到制造规则值,您需要能够以最高自动化水平运行DFM。 DFM验证工具使用“设计中心”概念来允许自定义DFM流程,属性映射,组件分类以及制造规则文件的设置和管理。使用分层方法,您可以使用驱动派生规则模型的常量和变量来创建主规则模型。这大大降低了DFM环境的支持要求。

它甚至提供符合IPC-7351标准的默认主机集。

了解制造风险

DFM验证工具不仅可以识别PCB设计在哪些地方严重违反了供应商的制造能力,还可以通过使用红色,黄色和绿色的颜色严重性指示器显示在哪里可能发生良率或现场故障问题。 DFM验证可以进一步对问题进行排序和优先级排序,以便您可以轻松地解决最关键的问题。分配给每张支票的权重是用户可定义的,使您可以对结果的优先级应用标准。毕竟,您的技术和供应商的流程可能与另一家公司的流程不同。

2、准备制作

制造和制造一直是PCB设计不可或缺的一部分。 以前,设计师使用多个应用程序来创建原理图,布局并准备制造。 为了简化过程,Xpedition集成了制造准备环境,用于制造数据创建,生成和验证。

制造准备工作使设计人员可以在板级或面板级控制其制造数据,从而确保设计和制造数据的完整性。

制作准备工作提供了独立的面板创建和编辑环境,可使用面板设计数据库在面板级别创建制造数据。 它还提供了附加的板级功能,包括详细的数据视图,可搜索的PDF输出,铜平衡,数据输出和Gerber In / Drill In功能。

七、自动化

自动化在设计和布局产品中提供自定义和可扩展性,从而允许添加自定义功能,重复性任务的自动化,以及能够针对客户特定用例量身定制流程并针对专用流程优化流程的能力。使用多种行业标准语言(VBscript,Jscript,TCL,Java,VB6,C ++,C#,VB.NET ...)可最大程度地缩短公司程序员的启动时间,并有助于脚本重用。自动化的结果是减少了错误,提高了生产率,提高了设计的性能,质量和可靠性,降低了设计成本,并缩短了上市时间(并缩短了获利时间)。

八、知识产权管理

数据管理系统将电子设计流程引入供应链,并将供应链引入设计者的桌面。它可确保整个设计过程中完整的数据一致性,准确性和可用性。

此外,它整合了多个数据系统,以便跨多个团队成员,学科和站点进行协作和生命周期管理。

它通过将设计数据管理与组件信息集成在一起来做到这一点,以便可以在桌面上轻松获得公司组件采购策略(批准的零件,首选的供应商)。

这可以帮助设计人员在设计过程中进行最佳的组件选择和管理零件清单,从而可以将它们作为准确的BOM满足企业在成本,可靠性和法规遵从性方面的公司政策而发布。

在项目结束时,它会管理流程,以便可以将准确的产品文档发布到企业制造,PLM和ERP系统以及供应链管理系统。

设计重用

在中央库中创建和存储可重用的电路块,包括原理图以及PCB放置和布线数据。然后,现在和将来都可以将它们放置在同一设计或多个设计中并进行修改。设计重用可自动执行此过程并管理设计数据,以确保无错误的数据库并无需重新设计同一电路,从而缩短了总体PCB设计周期。布局数据也可以轻松地在设计中和其他设计中剪切/粘贴,从而可以非正式地重用设计的各个部分。

变体管理

变量管理器处理从单个设计数据库创建多个产品配置的过程。 方案经理的单点ECO管理可最大程度减少错误,降低成本,提高设计质量并提高生产效率。

九、支持,教育和咨询

Mentor Graphics通过Xpedition流程工具提供全方位的服务,以提高您的生产率和成功率。 客户支持提供屡获殊荣的技术支持,创新的电子支持和高质量的产品增强功能。

教育服务提供课堂和在线培训,以帮助您将新工具和技术吸收到您的设计环境中。 最后,Mentor Consulting随时准备在艰难的设计领域提供专门的专业知识。

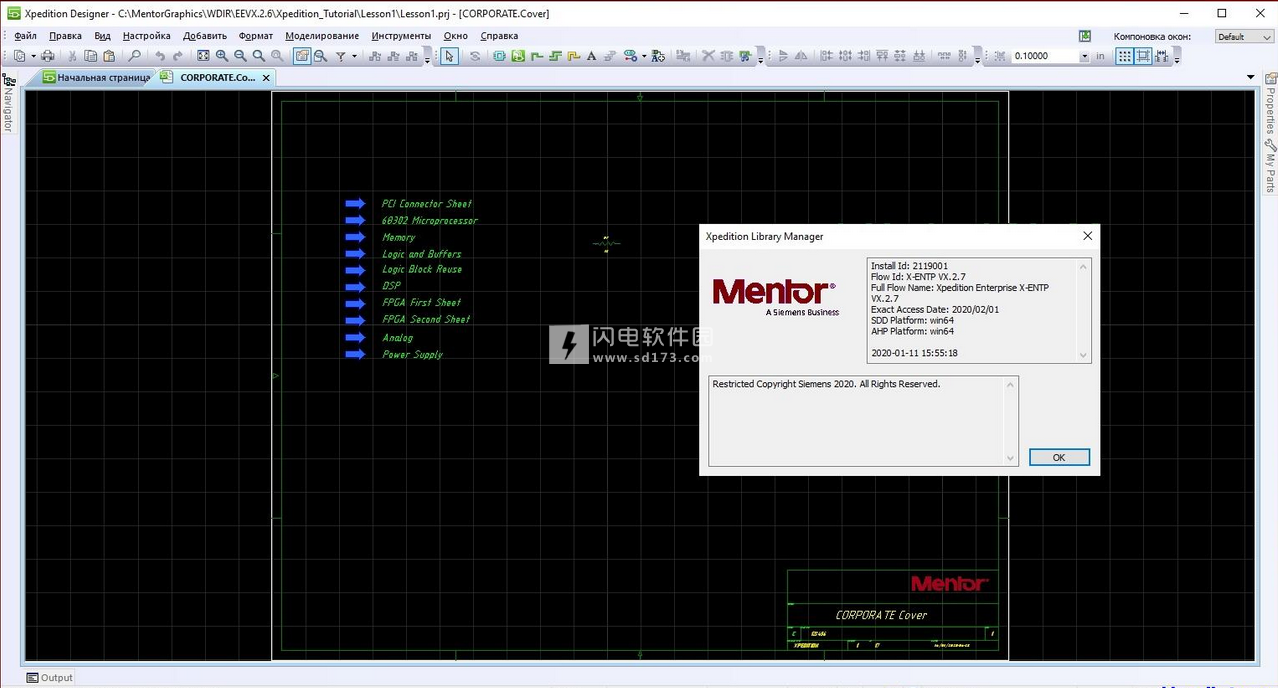

安装破解说明

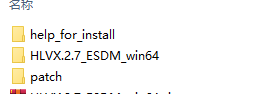

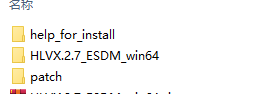

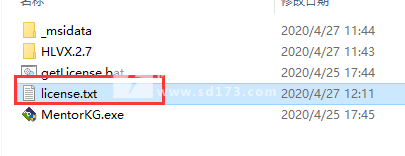

1、根据需要下载并解压,如图所示,

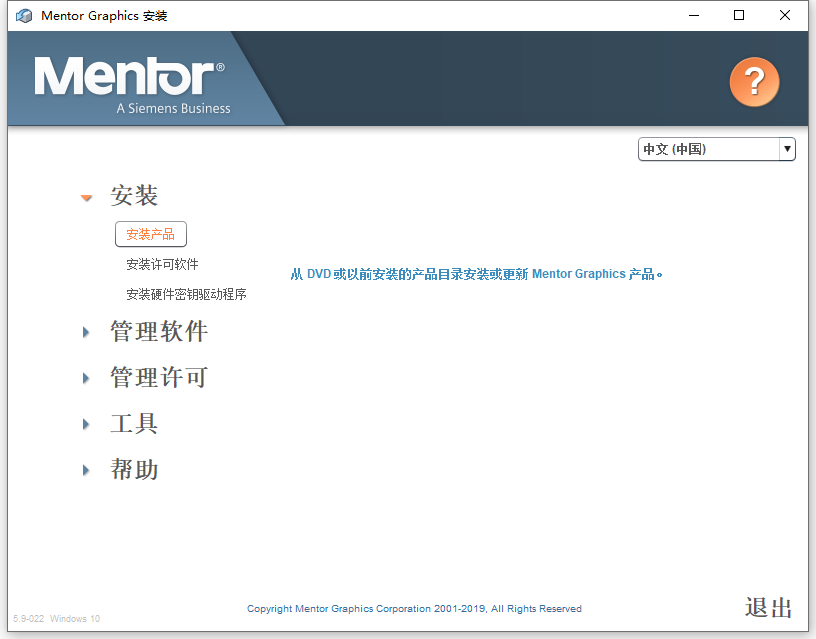

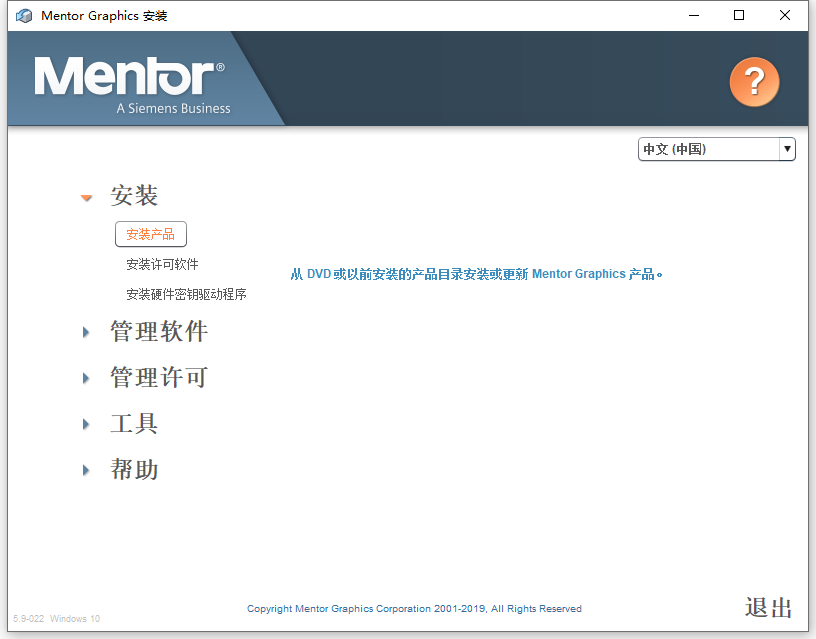

2、解压安装程序,双击setup.exe安装,点击安装产品

3、选择安装位置和安装产品

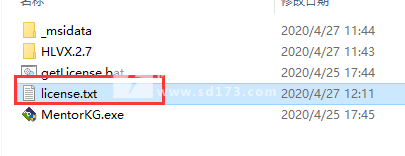

4、安装即将完成的时候,出现许可证向导窗口,这时候将patch\Xpedition Enterprise X-ENTP VX.2.7 patch中的getLicense.bat和MentorKG.exe复制到默认C:\Mentor Graphics中,然后运行getLicense.bat,将生成license.txt,保存到默认C:\MentorGraphics中

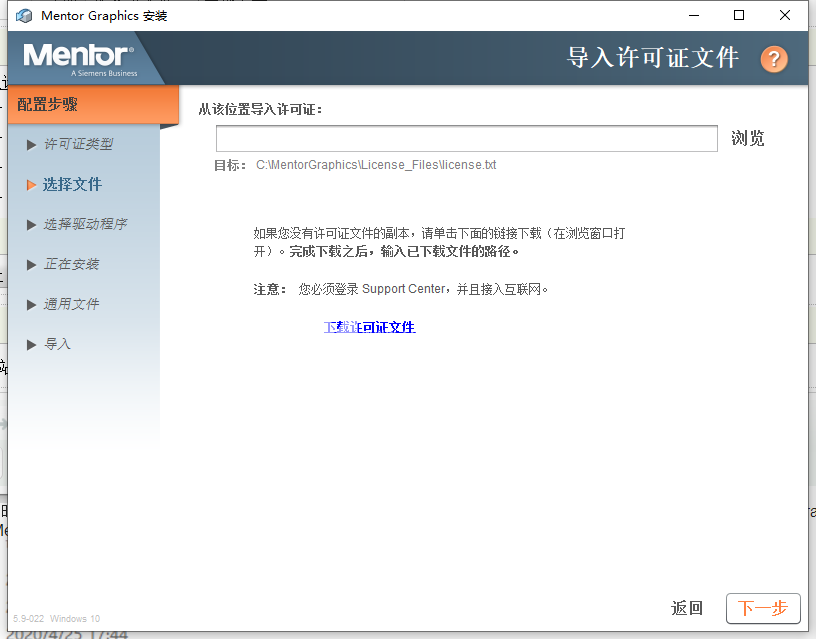

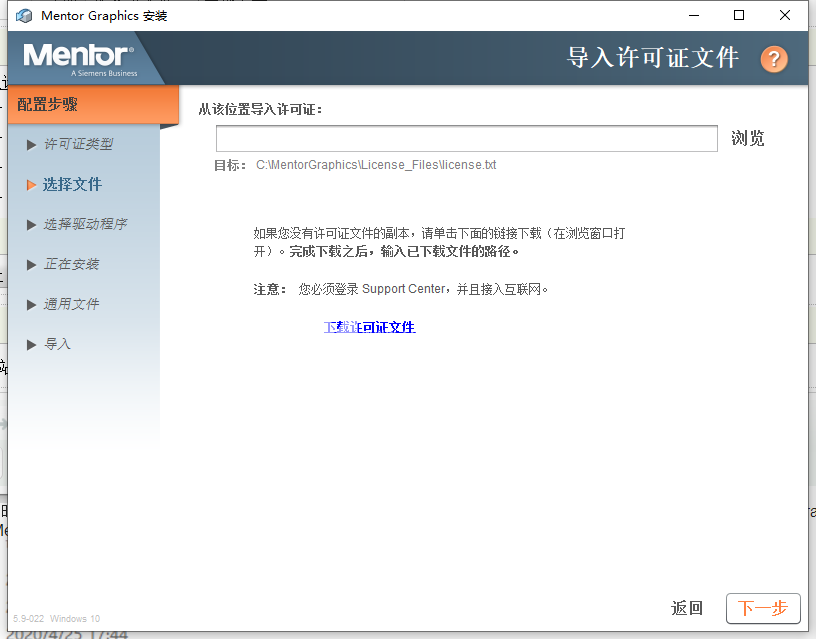

5、选择我想继续执行许可设置”,单击“下一步” ,在新打开的窗口中,点击浏览按钮并选择默认C:\MentorGraphics\ license.txt

6、打开破解文件夹,patch\Xpedition Enterprise X-ENTP VX.2.7 patch,将EEVX.2.7文件夹复制到安装目录中,替换目标中的文件

7、最后,将ByYLYN.bat复制到安装目录中,默认C:\MentorGraphics,管理员身份运行

Вводные:

1) Установка осуществлялась в среде Windows 10x64, т.е. про возможные нюансы и отклонения процесса в W7 и W8 не подскажу;

2) Сам по себе процесс установки очень схож с тем как это протекало в более ранних версиях и даже как оно показано на видео.

Итак:

1) Запускаем Setup.exe из "Ваше_место_хранения_скачанных_торрентов"_EEVX.2.7\XENTPVX.2.7_win64\;

2) В окне инсталлятора выбираем (галочками в чек боксах) нужные в будущей работе компоненты;

3) Терпеливо ждём, попутно наблюдая, как скрипты инициализируют установку всяких визуалС и т.п.;

4) Ближе к завершению установки процесс выведет окно License Wizard с двумя сакраментальными вопросами, верхний - "I would like continue through the licensing setup", нижний - "I have a valid license. I would like to skip the licensing setup.";

5) Здесь остановитесь, лучше закинте в корень созданной инсталлятором директории C:\Mentor Graphics из "Ваше_место_хранения_скачанных_торрентов"_EEVX.2.7\Xpedition Enterprise X-ENTP VX.2.7 patch\ файлы getLicense.bat и MentorKG.exe (т.е. ,будет так: C:\Mentor Graphics\getLicense.bat и C:\Mentor Graphics\MentorKG.exe);

6) Запустите из C:\Mentor Graphics\ батник getLicense.bat (см. п.5). Откроется командная строка и ВНИМАНИЕ, без вывода на экран блокнота, сразу (ну там минута - две) сохранит целевой файл лицензии рядом со своим расположением т.е C:\Mentor Graphics\license.txt. Расширение можно не менять;

7) Возвращаемся к п.4 и в указанном (должно висеть на экране, мы же остановились...) окне устанавливаем точку в верхнем чекбоксе с вопросом "I would like continue through the licensing setup", жмём Далее;

8) Во вновь открывшемся окне с вопросом о расположении файла лицензии, используя кнопку browse, указываем - C:\Mentor Graphics\license.txt. жмёд Далее;

9) Во вновь открывшемся окне с вопросом о том, где будет располагаться рабочая директория WDIR, либо соглашайтесь с дефолтным, либо придумываете что-то своё и указываете инсталлятору этот путь. И по традиции жмём Далее;

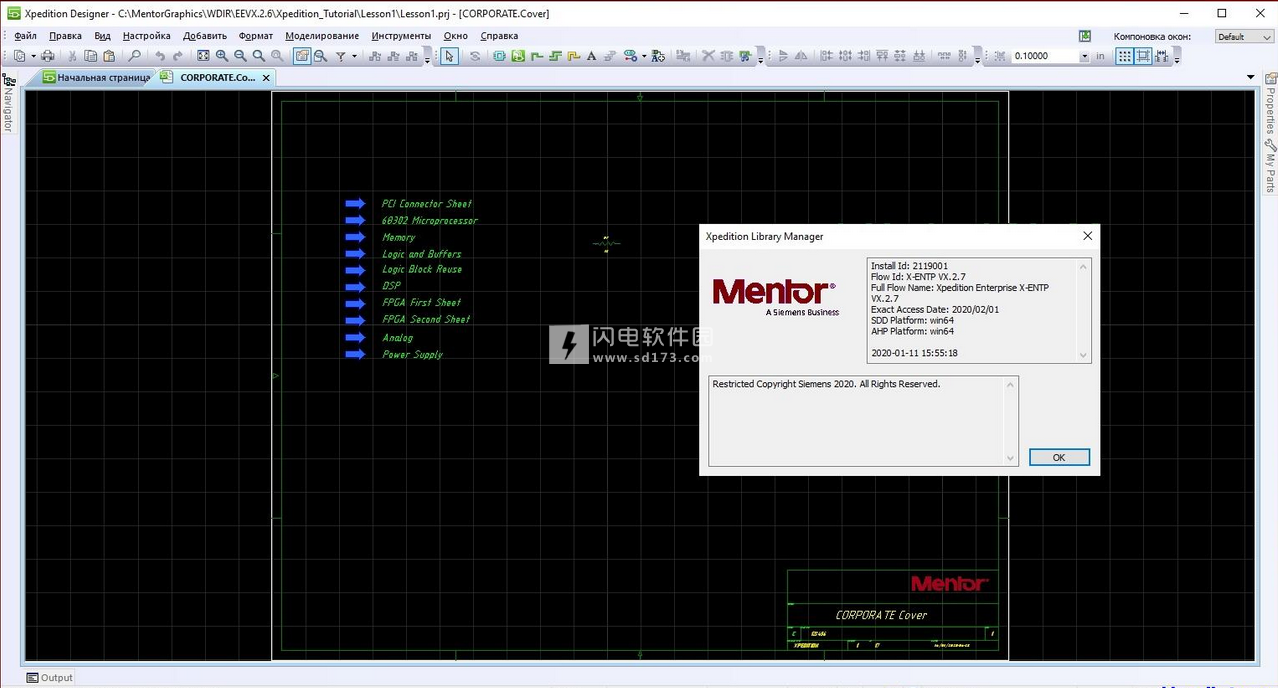

10) Доустанавливаем софт. Проверяем, что получилось в области лицензирования. Проявляем каким-либо способом скрытые папки (Total Commander наше всё, не реклама), теперь идём c:\ProgramData\mgcSDD\win64\ и видим там среди прочего license.txt, улыбаемся не веря своему счастью;

11) Теперь идём "Ваше_место_хранения_скачанных_торрентов"_EEVX.2.7\Xpedition Enterprise X-ENTP VX.2.7 patch\ копируем в буфер папку EEVX.2.7

sc01, идём в c:\MentorGraphics\ и выгружаем туда содержимое буфера со слиянием и заменой;

12) В самом конце установки идём в "Ваше_место_хранения_скачанных_торрентов"_EEVX.2.7\ и копируем в буфер ByYLYN.bat, идём в c:\MentorGraphics\ и выгружаем туда из буфера этот батник. Запускаем ByYLYN.bat оттуда, Вам покажется, что ничего не произошло, но это не так, ещё раз рассмотрите

sc02 и прочитайте на нём текст (это IMHO, но думаю так и есть);

13) И так процесс лицензирования Вами пройден (я надеюсь). В меню пуск должен, при удачном раскладе, появиться этакий перечень:

sc03, sc04, sc05, sc06

Подводные камни (мои). Добавил в Dashbord проект созданный и успешно трассированный в предыдущей версии софта. Содержимое старой WDIR\EEVX.2.6\ частично (*.xml и ещё по мелочи) закинул в WDIR\EEVX.2.7\. Запустил в xdx designer проектик, из него через инструменты открыл Layout, а он и говорит приблизительно - у вас мол нет лицензии и всё такое. Ну я подрасстроился, позакрывал все окна зашёл в C:\Mentor Graphics\ и запустил getLicense.bat ещё раз. Лицензия осталась в том же весе, поменялось время создания само собой. Больше никаких манипуляций (конфигуратор не запускал). При следующем открытии проекта (см. выше) - всё ОК и в xdx designer и в Layout.

Надеюсь кому-то помог.

闪电小编说明:

Xpedition Enterprise流程提供了从概念到制造交接的干净,集成的设计系统。 从系统定义和仿真到原理图输入,约束定义,布局,验证,可制造性设计,设计数据打包(从移交到PCB制造)的各个方面均可使用工具。从系统设计到最后的制造,独有的行业技术,强大的能力,通用的数据库和友好的用户界面,轻松消除使用方面的负担,全新全意进行设计和分析!全面满足用户的产品需求,最先进的制造技术、广泛的协作,专注于复杂的系统!通过强调易用性和团队生产力来解决当今高级系统设计日益复杂的问题。Xpedition提供了创新技术,这些技术认识到设计重用的重要性,自动化高速拓扑的布局,促进高级约束的配置,启用3D刚柔结构的设计和验证,并为库和设计提供强大的数据管理。

Mentor Graphics Xpedition Enterprise VX.2.13

Mentor Graphics Xpedition Enterprise VX.2.13

Mentor Graphics Xpedition Enterprise VX.2.13

Mentor Graphics Xpedition Enterprise VX.2.13