Synopsys FPGA P-2019ЪЧЬсЙЉСЫЭъећЕФНтОіЗНАИЃЌБОВњЦЗЬзМўПЩАяжњгУЛЇИќКУЕФНјааЕчТЗЕФЩшМЦКЭБрГЬЃЌгУЛЇгбКУЕФдаЭПЊЗЂЙЄОпЃЌПЩжБНгДгRTLдДДњТыКЭASIC IPжаЪЙгУЁЃЬсЙЉДгМЦЛЎЕНзлКЯЕФМЏГЩFPGAЩшМЦСїГЬЃЌЬсЙЉгУгкИпМЖFPGAКЭЛљгкFPGAЕФдаЭЕФПьЫйЃЌПЩППЕФТпМзлКЯНтОіЗНАИЃЌПЩздЖЏВЩгУЖржжГЩЪьЕФЗНЗЈРДМѕЧсШэДэЮѓЃЌР§ШчЕЅЪТМўЗзЊЃЈSEUЃЉЃЌетаЉЮЪЬтдкзюаТЕФFPGAЙЄвеМИКЮжадНРДдНЖрЕиГіЯжвдМАЬсЙЉРрЫЦгкFPGAгВМўВйзїЕФПЩЪгадЃЁгЩгкУПИіЙ§ГЬНкЕуЕФШнСПдіМгКЭЙІТЪНЕЕЭЃЌПЩБрГЬаОЦЌЕФЪЙгУдНРДдНЖрЁЃЩшМЦЪІЯждке§УцСйвЛаЉбЯОўЕФаТЬєеНЁЃР§ШчЃЌ28nm FPGAОпгаЯрЕБгк5000ЭђИіASICУХЕФШнСПЃЌетЭЦЖЏСЫЖдЙІФмИќЧПДѓЕФзлКЯЙЄОпЕФашЧѓЁЃSynplifyзлКЯЙЄОпЮЊЩшМЦШЫдБЬсЙЉСЫПЩЬсЙЉздЖЏЛЏЃЌИќПьЕФжмзЊЪБМфЃЌИќПЩдЄВтЕФЪБађЪеСВЃЌИпПЩППадЩшМЦЃЌЕчдДЙмРэЃЌЯШНјЕФбщжЄММЪѕвдМАаэЖрРДдДЕФIPМЏГЩЕФЗНЗЈЁЃSynplifyЙЄОпМЏПЩздЖЏжДаааэЖрЙІФмЃЌвђДЫЩшМЦШЫдБПЩвдзЈзЂгкздМКЕФВњЦЗВювьЛЏЃЌЭЌЪБТњзуНјЖШКЭГЩБОФПБъЁЃЦЦНтАцБОЯТдиЃЌКЌАВзАМЄЛюНЬГЬЃЌЛЖггаашвЊЕФХѓгбРДБОеОЯТдиЬхбщЃЁ

ЙІФмЬиЩЋ

вЛЁЂSynplify Pro

FPGAЩшМЦЕФТпМзлКЯ

SynplifyPro®FPGAзлКЯШэМўЪЧгУгкЩњВњИпадФмКЭИпадМлБШFPGAЩшМЦЕФаавЕБъзМЁЃSynplifyШэМўжЇГжзюаТЕФVHDLКЭVerilogгябдНсЙЙЃЌАќРЈSystemVerilogКЭVHDL-2008ЁЃИУШэМўЛЙжЇГжРДздЖрИіFPGAЙЉгІЩЬЕФFPGAЬхЯЕНсЙЙЃЌАќРЈAlteraЃЌAchronixЃЌLatticeЃЌMicrosemiКЭXilinxЃЌЫќУЧОљРДздЕЅИіRTLКЭдМЪјдДЁЃSynplify ProШэМўЪЙгУЕЅИівзгкЪЙгУЕФНчУцЃЌВЂФмЙЛжДаадіСПзлКЯКЭжБЙлЕФHDLДњТыЗжЮіЁЃ

ЖдгкашвЊОЁПЩФмПьЕФзлКЯдЫааЪБМфКЭзюИпжЪСПЕФЪБађЃЌУцЛ§КЭЙІКФНсЙћЕФДѓаЭЩшМЦЕФЩшМЦШЫдБЁЃSynplify®PremierШэМўЬсЙЉСЫSynplify ProЕФЫљгаЙІФмвдМАвЛећЬзгУгкИпМЖFPGAЩшМЦЕФЙЄОп

1ЁЂдіСПЃЌЛљгкПщЕФКЭздЯТЖјЩЯЕФСїГЬЃЌДгвЛДЮдЫааЕНЯТвЛДЮдЫааПЩЛёЕУвЛжТЕФНсЙћ

2ЁЂздЖЏБрвыЕудіСПСїПЩНЋдЫааЪБМфЬсИпЖрДя4БЖЃЌЭЌЪББЃГжQoR

3ЁЂМгЫйдЫааЪБМфЃЌзюЖржЇГж4ИіДІРэЦї

4ЁЂНХБОКЭTcl/FindжЇГжСїГЬздЖЏЛЏвдМАПЩздЖЈвхЕФзлКЯЃЌЕїЪдКЭБЈИцЙІФм

5ЁЂЪЙгУAchronixЃЌAlteraЃЌLatticeЃЌMicrosemiЃЌXilinxЕФFPGAЛёЕУзюМбУцЛ§КЭЪБађНсЙћ

6ЁЂЗжВуЭХЖгЩшМЦСїГЬЃЌдЪаэВЂааКЭ/ЛђЕиРэЗжВМЕФЩшМЦПЊЗЂ

7ЁЂШЋУцЕФгябджЇГжЃЌАќРЈVerilogЃЌVHDLЃЌSystemVerilogЃЌVHDL-2008КЭЛьКЯгябдЩшМЦ

8ЁЂFSMБрвыЦїКЭFSM ExplorerЃЌгУгкДгRTLздЖЏЬсШЁКЭгХЛЏгаЯозДЬЌЛњ

9ЁЂЭМаЮзДЬЌЛњВщПДЦїПЩздЖЏДДНЈЦјХнЭМвдЕїЪдКЭМЧТМFSM

10ЁЂздЖЏДцДЂЦїКЭDSPЭЦРэПЩздЖЏЪЕЯжЩшМЦЃЌВЂОпгазюМбЕФУцЛ§ЃЌЙІКФКЭЪБађжЪСП

11ЁЂгУгкЗжЮіЕФдіСПОВЬЌЪБађдЪаэИќаТЪБађвьГЃдМЪјЃЌВЂПЩвдСЂМДВщПДНсЙћЃЌЖјЮоашжиаТКЯГЩ

12ЁЂHDL AnalystНЛЛЅЪНЭМаЮЗжЮіКЭЕїЪдЙЄОпЃЌгУгкЩшМЦеяЖЯЃЌЮЪЬтИєРывдМАЙІФмКЭадФмЗжЮі

ЖўЁЂSynplify Premier

МгПьFPGAЩшМЦКЭЛљгкFPGAЕФдаЭЕФЪЕЯж

SynplifyPremier®ЪЧвЕНчзюЯШНјЕФFPGAЩшМЦКЭЕїЪдЛЗОГЁЃSynplifyзлКЯЙЄОпЬсЙЉСЫПьЫйЕФдЫааЪБМфЃЌадФмЃЌгУгкГЩБОКЭЙІКФНЕЕЭЕФЧјгђгХЛЏЃЌЖрFPGAЙЉгІЩЬжЇГжЃЌдіСПКЭЭХЖгЩшМЦЙІФмЃЌвдМгПьFPGAЩшМЦПЊЗЂЕФЫйЖШЁЃSynplify PremierАќКЌЕФЙІФмПЩздЖЏДДНЈИпЖШПЩППЕФЩшМЦЃЌР§ШчгУгквНСЦЃЌЦћГЕЃЌЙЄвЕздЖЏЛЏЃЌЭЈаХЃЌОќЪТКЭКНПеКНЬьгІгУЕФЩшМЦЁЃ

PremierАќКЌIdentify InstrumentorЃЌвдЬсЙЉвЛжжвзгкЪЙгУЕФЗНЗЈРДВщевдкАхЩЯдЫааЕФFPGAЩшМЦжаЕФЙІФмДэЮѓЁЃИУНтОіЗНАИЮЊФЃФтЦїЬсЙЉСЫЖдвбЪЕЯжЕФFPGAгВМўЕФПЩЪгадЃЌВЂВщПДСЫжБНгЕўМгдкRTLДњТыЩЯЕФдЫаажаЕФFPGAЕФЪЕМЪаХКХжЕЁЃетбљЃЌгУЛЇПЩвдвдФПБъВйзїЫйЖШжДааЯЕЭГФкЕїЪдЁЃ

PremierжМдкНгЪмгХЛЏЕФRTLЃЌЕкШ§ЗНКЭФкВП/ЯШЧАПЊЗЂЕФIPЃЌДгЖјПЩвдНјааЙуЗКЕФЩшМЦЬНЫїКЭИќПьЕФЪЕЪЉЁЃ

ДЫЭтЃЌSynplifyМЏГЩСЫЖдDesignWare®IPЃЌIdentify RTL DebuggerЃЌVCS®ИпадФмЙІФмбщжЄЕФжЇГжЃЌвдМАгыASICМцШнЕФзлКЯСїГЬЃЌПЩгУгкДДНЈЛљгкFPGAЕФдаЭЁЃ

1ЁЂздЖЏУХПиЪБжгзЊЛЛЃЌжЇГжЛљгкFPGAЕФдаЭЩшМЦ

2ЁЂМЏГЩЕФIdentify RTLЕїЪдЦїЃЌПЩПьЫйЗЂЯжЙІФмДэЮѓ

3ЁЂздЖЏЛЏЩшМЦЪЕЯжСЫИпПЩППадКЭАВШЋаджСЙиживЊЕФЩшМЦЃЌАќРЈDO-254ЃЌISO 26262КЭIEC 61508

4ЁЂгыVCS SimulatorМЏГЩВЂжБНгжЇГжDesignWare IP

5ЁЂЪБађадФмКЭУцЛ§/ГЩБОНЕЕЭЕФзюМбНсЙћжЪСПЃЈQoRЃЉ

6ЁЂЗжВМЪНзлКЯЃЌжЇГжЕЅЛњЛђЖрЛњзлКЯ

7ЁЂМгЫйЕФдЫааЪБЬсЙЉЖрДя3БЖЕФдЫааЪБЃЌУПИіаэПЩжЄзюЖржЇГж4ИіДІРэЦї

8ЁЂздЖЏДцДЂЦїКЭDSPЭЦРэПЩЬсЙЉзюМбЕФЧјгђЃЌЙІТЪКЭЪБађжЪСП

9ЁЂжЇГжVHDLЃЌVerilogЃЌSystemVerilogЃЌVHDL-2008КЭЛьКЯгябдзлКЯЕФЙуЗКгябд

10ЁЂЭЈЙ§HDL AnalystКЭЗжВуЕїЪдСїГЬНјааИпМЖЩшМЦЕїЪдКЭеяЖЯ

SynopsysЕФ ЛљгкFPGAЕФдаЭПЊЗЂНтОіЗНАИ ЫѕЖЬСЫВњЦЗЩЯЪаЪБМфЃЌВЂЭЈЙ§жЇГждчЦкЧЖШыЪНШэМўПЊЗЂВЂдЪаэдкаОЦЌжЦдьжЎЧАОЭНјааШэгВМўаЭЌЩшМЦЃЌДгЖјБмУтСЫАКЙѓЕФЩшБИжиаТЩшМЦЁЃГ§СЫЭъШЋМЏГЩЕФЃЌЛљгкFPGAЕФдаЭПЊЗЂНтОіЗНАИжЎЭтЃЌSynopsysЛЙЮЊЛљгкFPGAЕФдаЭПЊЗЂШЫдБЬсЙЉСЫвЛЬзЙЄОпЃЌвдЙЙНЈздМКЕФПЊЗЂАхЃЌSynplify PremierЮЊASICКЭSoCЩшМЦШЫдБЬсЙЉСЫЖржжЙІФмЃЌгажњгкМгЫйАыЕМЬхдаЭЕФПЊЗЂЁЃЩшМЦШЫдБУцСйЕФЪзвЊЬєеНжЎвЛЪЧИќЛЛЩшМЦжаЗЧЛљгкFPGAЕФВПЗжЃЌР§ШчДцДЂЦїЃЌЪБжгХфжУКЭASICВтЪдЕчТЗЁЃSynplify PremierГ§СЫНтЮіЖржжгябдИёЪНКЭдМЪјЮФМўЭтЃЌЛЙЬсЙЉСЫвЛжжгУгкДІРэИЈжњЮФМўЕФМђБуЗНЗЈЁЃЯТвЛИіЬєеНЪЧЕкШ§ЗНЃЌSynopsysКЭФкВППЊЗЂЕФIPЕФЕМШыКЭДІРэЃЌSynplify PremierПЩвдЪЕЯжздЖЏЛЏвдДѓДѓЬсИпЩњВњТЪЁЃзюКѓЃЌSynplify PremierЪЙЪБжгзЊЛЛздЖЏЛЏЃЌДгЖјЪЙASICЩшМЦЪЪКЯFPGAЕФЪБжгНсЙЙЁЃ

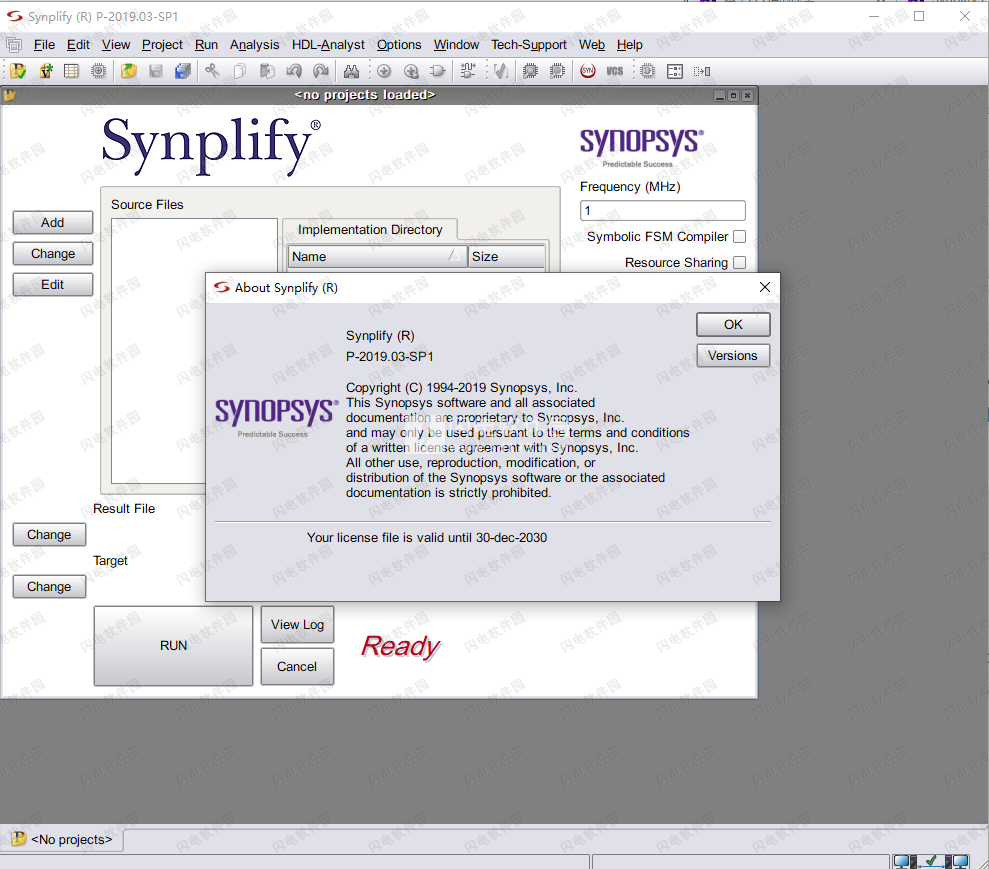

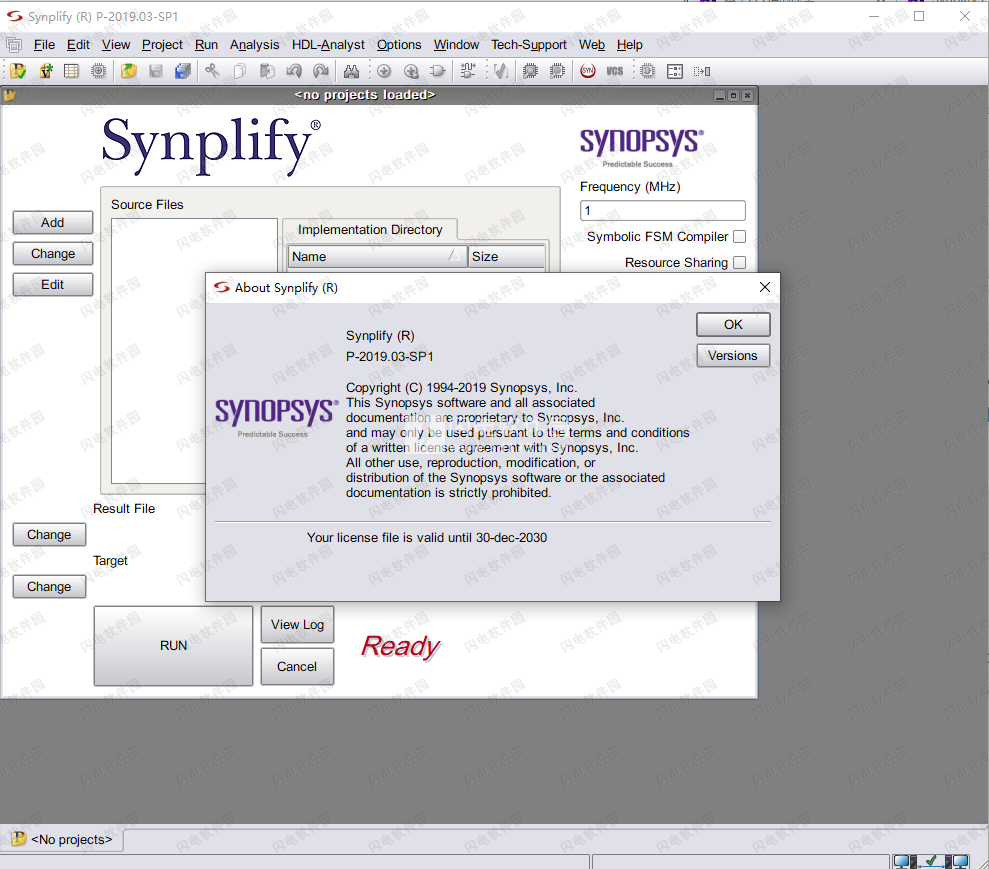

Synopsys FPGA P-2019.03-SP1

Synopsys FPGA P-2019.03-SP1

Synopsys FPGA P-2019.03-SP1

Synopsys FPGA P-2019.03-SP1