Cadence Sigrity是一款用于高频电路中的仿真和信号完整性的软件。提供更多的功能和工具,旨在轻松迎接更快的处理需求,以更高的处理速度和更高的频率工作更快的电路。通过提高速度信号以准确加快安装在电路板PCB或电路板上层压板上的路线上的信号,以及在现场情况下出现新问题,被卡住的工程师会遇到诸如干扰,失真和噪声以及高信号完整性等事件。频率导致受到威胁。使用可在初始阶段检查各种情况,从而使准确的设计和重新设计的可能性降至最低。该软件支持直接在Allego数据库的PCB和IC设计上进行读写。基于SPICE的精确模拟器以及用于2d和3d的内置求解器可以提取用户。该软件还对晶体管级输入和输出功能进行了建模,其中包括功耗感知的IBIS 5.0支持。

1、高级套装eXtractor

推出高级套装eXtractor

(新)Sigrity Advanced Package eXtractor是本版本中引入的一项新技术。它可以让您更准确地创建RLGC或SPICE IC封装的电气模型,并且比其他方法快十倍。这是通过使用Cadence先进的封装仿真技术实现的。Advanced Package eXtractor中这些求解器衍生的紧凑型模型允许您执行系统级信号和电源完整性模拟,包括驱动器、接收器和互连。

2、宽带SPICE

具有被动模式IV的BBS引擎

(新增)Passivity mode IV已添加到Broadband SPICE中,您可以在选项窗体的提取设置中选择Passivity mode IV选项。此模式支持BBS提取引擎。它采用了先进的矢量拟合和被动强制方法,有助于在BBS引擎中获得具有复杂低频行为的S参数的精确拟合模型。

3、PowerDC

多板限流IR跌落分析

(新增)PowerDC增加了一个新的工作流程,即多板限流IR Drop Analysis。它将帮助您对多个板执行当前有限的IR压降分析。

按网络分组分布图结果

(新增)要按网络对分布图结果进行分组,请在“选项”窗体中选中“每个电源一张图,地面一张图”复选框。这将有助于您检查报告中的热点/冷点。

电阻测量向导修订

(新)仅测量电源或接地网从一个部件到另一个部件的电阻。在设置电阻测量向导中,从集中到集中(部分/回路)、集中到多个(部分/循环)、多个到集中(局部/回路)和多个到多个中选择一个电阻网络拓扑。

在多板工作流中同时打开多个窗口

(新增)现在在一个单独的窗口中打开每个布局块,而且最多可以同时打开三个窗口。修改设计设置并在这些窗口中查看结果。在块上单击鼠标右键,然后选择“在新窗口中加载”以打开新窗口

4、PowerSI

使用PowerSI中的Clarity 3D-IE解算器生成准确的结果

(新增)在PowerSI中,您现在可以使用Clarity 3D-IE解算器功能生成准确的模拟结果,同时为平行选项卡轨迹创建切割多边形。要执行此操作,请在“选项”对话框的“特殊处理”页面中选中“启用切割Clarity Block(需要Clarity 3D-IE许可证)”复选框。要为平行制表符轨迹创建切割多边形,必须检查以下条件:

每个多边形中的过孔、焊盘、引线或引线不应接触所选网络的接线片轨迹。

每个选定的网应该只有两个与切割多边形的交点。

轨迹的任何部分都不能同时落在两个或多个切割多边形中。

5、SPEEDEM

对SPEEDEM的高性能计算(HPC)支持

(新增)为了遵守HPC法规,SPEEDEM中的所有工作流都将使用第二代许可证来加快模拟过程。为此,一个名为“设置计算机资源”的新工作流项目已添加到仿真模式中。

6、XcitePI

端口和探头设置

(新增)在工作流窗格的“输出设置”下添加了两个新选项,端口和探测器。选择这些选项可以指定回路的端口或探针设置。

在XcitePI中加载GDS文件

(新增)在将GDS文件加载到XcitePI之前,在GDS文件上执行各种操作,如从日志文件加载设置、修改图层映射文件的文件路径等。这将允许在XcitePI中更容易地打开文件,这与Gds到Spd转换器更一致。

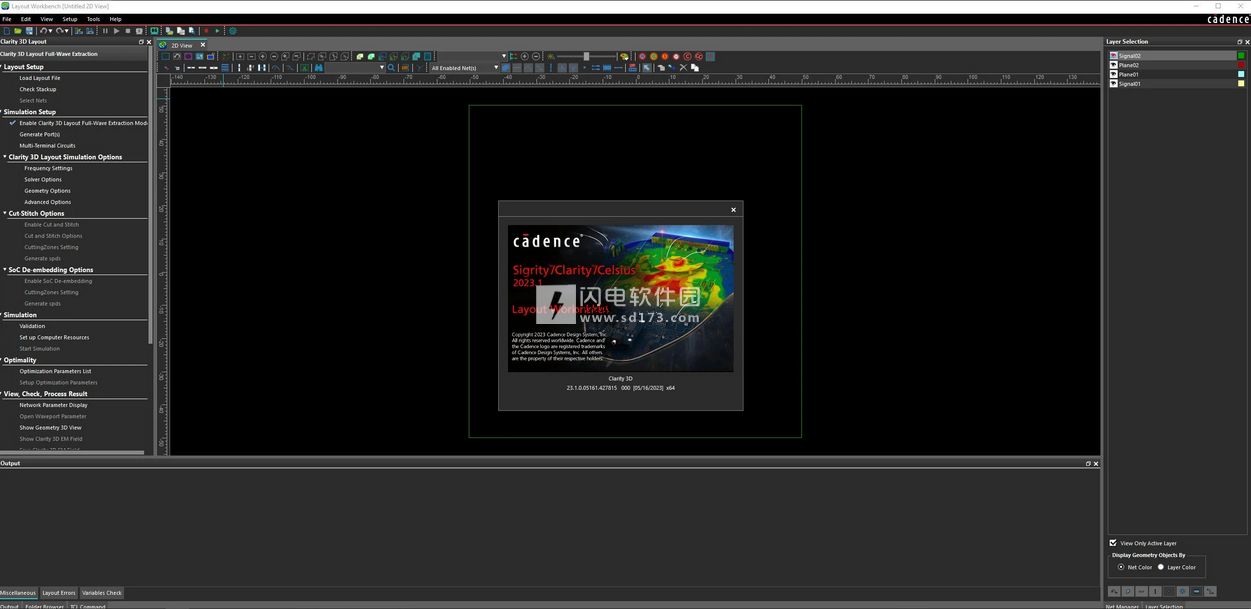

7、布局工作台

Python命令

(新增)使用Python命令自动执行Layout Workbench工具中的任务。Python是一个简单易用的平台,它为使用Tcl无法完成的任务提供了Layout Workbench功能。为此添加了一个新的窗格Python命令。

改进的图形用户界面

(测试版)在“选择许可证套件”对话框中添加了一个新选项“启用新UI/UX”,允许您打开改进的Layout Workbench GUI。在新的GUI中,工具栏图标得到了增强和重新排列。此外,在GUI的右侧添加了新按钮,允许您在GUI中显示或隐藏相关窗格。

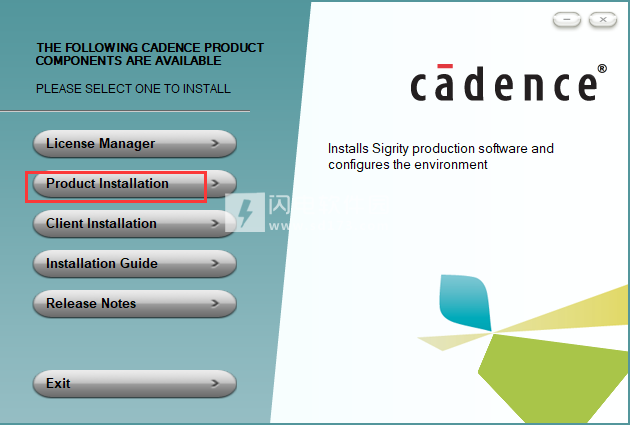

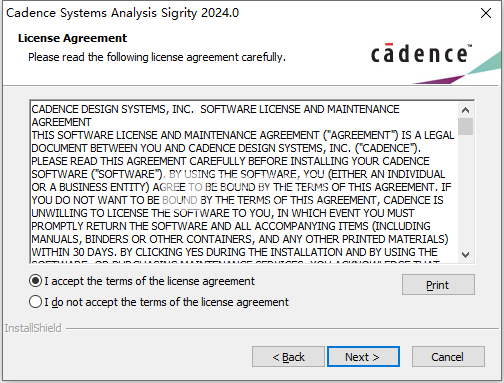

Cadence Design Systems Analysis Sigrity 2024.1 HF002 x64

Cadence Design Systems Analysis Sigrity 2024.1 HF002 x64

Cadence Design Systems Analysis Sigrity 2024.1 HF002 x64

Cadence Design Systems Analysis Sigrity 2024.1 HF002 x64