Pulsonix10.5破解版是先进的PCB设计软件,使用旨在为用户带来简化的流程以及智能的自动化解决方案,丰富灵活的选项,让您轻松获得无限的可能,使用能够混合和匹配设计和设计项目的不同方面,以根据尽可能多的现有设计数据来生成布局。产品涵盖原理图的设计创

Pulsonix10.5破解版是先进的PCB设计软件,使用旨在为用户带来简化的流程以及智能的自动化解决方案,丰富灵活的选项,让您轻松获得无限的可能,使用能够混合和匹配设计和设计项目的不同方面,以根据尽可能多的现有设计数据来生成布局。产品涵盖原理图的设计创建、基于业界领先的混合模式Spice的仿真、电路板布局工具、动布线和自动放置、交互式高速设计功能、高级组件和电路板技术选项等等,功能齐全,使用简单,改善您的电子设计流程,为您的公司提供先进但价格合理的PCB设计功能,10.5新版本带来更多的功能,欢迎有需要的朋友来本站下载体验!

10.5新功能

1、3D视图

对STEP 3D Preview功能进行了许多增强:

新的测量选项允许两个3D项目之间的距离以测量尺寸的形式显示在STEP 3D Preview中。

在3D预览中插入冲突标记以指示项目之间发生冲突的位置。

STEP 3D中的新分解图,各层之间分开显示内部层结构。

可调聚光灯位置。

现在可以选择机箱是否包含在STEP 3D中。

保存机箱位置更改。

选择STEP 3D中包含的图层。

透明板。

现在,在库管理器中具有单独的“STEP模型文件夹”选项卡。

在STEP 3D Preview中更好地支持3D Space Mouse。

2、原理图设计中的多连接

新的原理图交互式选项可简单地将多个符号引脚连接到另一个符号或总线段。您可以从一行组件引脚开始多个连接,也可以从总线中拉出连接。

从总线拉出时,连接之间的间隙将使用“连接默认值”对话框中的新“连接间隙”值。

另外,移动符号时,您现在可以将其放在总线段上,以将端子连接到总线。

3、原理图领域

现在可以在原理图设计中添加命名区域。这些是为新的“区域属性规则”添加的,这些新规则在原理图设计中使用,是一种在将项目转换为PCB或与PCB设计同步时向项目添加属性的快速而动态的方法。然后可以创建PCB设计中的规则以对这些属性起作用。区域属性规则还可用于将属性添加到块或块实例中的所有组件,网络或引脚。

原理图中的区域还可以在“查找”中使用,以快速找到设计的特定区域,并在CAM/绘图中使用,以仅绘制指定区域内的项目。

命名区域也可以在原理图文档符号中定义,用于在添加到原理图设计时定义绘图区域。

4、组件放置规则

在PCB设计中,您可以添加“组件放置”规则,这些规则定义组件必须保留或不进入的层和区域。组件将通过属性进行匹配。特别是,您可以使用新的逻辑示意图区域属性规则为此指定一个属性。

5、钻孔图层

现在,您可以定义钻取工程图图层,该图层将显示设计中的钻取符号和钻取ID。为此,您需要定义“钻探图”类型的图层类,然后将钻探图图层与该类关联,并设置其代表的“图层跨度”。

可以将文本,形状和插入的钻探表添加到这些层中,以代替现有的钻探图输出方法进行绘制。

现在,您可以为钻头尺寸分配颜色。演习ID字母和符号将以该颜色绘制。

可以在打击垫,安装孔上或通过使用新的<Drill Id>属性位置显示Drill Id字母。如果将其添加到新的钻孔图图层,它将替换在该图层上绘制的默认ID字母。如果ID字母与另一个项目太近,则可以重新放置它。

插入到“钻孔图”图层上的“钻孔尺寸表”将自动采用与该图层关联的“图层范围”,并且仅列出在该图层上显示的“钻孔”类型。

6、在适当位置编辑块实例符号

现在可以以与在原理图文档符号窗口中相同的方式在原理图设计文档中编辑生成的块符号(例如,插入/移动销,添加/编辑形状等)。这可以使用新的“在位编辑符号”命令来完成。

7、技术对话

款式

现在可以选择多种样式并将其合并为一种。

规则

增加了关闭单个规则的功能。

现在可以为规则添加注释。

规则注释和错误的单元格通知为彩色三角形。

新的原理图设计区域属性规则。有关详情,请参见上文。

新的PCB设计组件放置规则。有关详情,请参见上文。

间距规则

面板设计的其他设计级别间距。现在,您可以将Tab-Rout设置为Panel Edge,Tab-Rout设置为V-Score,V-Score设置为Drill Hole的最小间距。当使用设计规则检查来检查Tab-Routs和V-Scores时,将使用它们。

网络名称

基于Excel样式的通配符的过滤器已添加到“网络名称”页面。

添加了同时删除多个选定的未使用网络名称的功能。

层数

现在,在“层”对话框中,您可以将微型过孔上的焊盘与普通过孔分开隐藏。

新的图层类型“钻孔图”可用于图层类。然后,您可以使用新类定义钻取图纸图层,该类将显示钻取符号和设计中每个孔的钻取ID。

钻头尺寸

现在,您可以为“钻头尺寸”分配颜色。插入的“钻具表”中的钻具ID和符号均以该颜色绘制。

设计设定

设计设置命名页面中的新选项称为“填补数字范围的空白”。禁用此选项将强制将新组件,块,块实例,测试点,分支点和星形点的名称始终添加在当前在设计中的名称列表的末尾。

用于显示“网格”页面中的网格的大量嵌套复选框已由具有四个选项的单个下拉列表框取代。

8、产出

在“打印设置”中,您现在可以创建命名的输出设备,例如,您可以使用不同设置的“PDF颜色”和“PDF灰色”。然后可以将这些用于单个图。

面板编辑器中现在提供了DXF输出功能。

您可以在“绘图设置”中关闭CAM/绘图报告。

现在,“CAM/图”对话框中提供了更多类型的输出。现在,您可以创建图以生成DXF,ODB++,LPKF,IPC-2581,GenCAD,STEP和IDF输出。

现在,您可以在输出文件名模板中使用“图字符串”字段。

9、选项对话框

新的选择选项允许使用框架选择来选择构造线。

常规选项中的新设置,使您可以指定是否始终仅以视图形式打开PCB或原理图设计。此外,在“文件打开”对话框上,“打开”按钮现在具有一个下拉按钮,为您提供了额外的选项“仅打开视图”。

“显示隐含的连接点”已从“选项”移动到“设计设置”,因此每个设计现在都具有此标志。现在,可以使用“属性”关闭单个符号引脚上的“隐式连接”,例如,用于信号参考。

显示选项中新的Declutter选项可加快大型设计的重绘速度。

10、特性

现在,“尺寸标注”和“文本标注”的属性对话框将显示附件的附件信息。

文字标注现在可以具有自己的文字颜色和纯背景颜色。

添加了在位图属性中锁定纵横比的功能。现在,除非从上下文菜单中选中“自由宽高比”,否则在移动位图的一角时将保持宽高比。

现在,“过孔属性”的“附加轨道”部分报告了它是否已附加到其最高/最低层的模板/平面连接上。还有一个新列表,显示了Via附加在哪些层上。

各个文本标注现在可以具有自己的文本颜色和纯背景颜色。此功能使您可以通过选择文本标签(即标注)并使用“属性”更改标注颜色和“填充颜色”来增强插入的“叠层符号”的外观。标签所指向的层堆栈图中的框将以标注填充颜色绘制。

现在可以从一个块中删除已使用的块端口(前提是该块符号不是从库中删除的)。

使用“更改零件”对话框时(例如,从“组件属性”中获取),“查找范围:”库现在默认为所选零件的库,而不是“[所有库]”。

如果属性不是在组件上实际指定的,而是从这些来源之一衍生而来,则组件属性现在包括后缀“[Part]”或“[Symbol]”。

现在,您可以使用其“线段属性”对话框页面来更改选定圆或弧段的半径或直径。

现在,在“组件属性”对话框中,组件名称旁边有一个按钮。使用此命令可以使用相同的词干将名称更改为第一个免费组件名称。

11、相互作用

用于在PCB封装中插入表面贴装焊盘的新命令。还添加了默认页面,因此可以设置SMD Pad默认值。

在“重新生成模块符号”中添加了一个选项,以重置现有的引脚位置。选择“是”将根据引脚的类型排列所有引脚。选择“否”将使现有的引脚位置保持不变,并排列新的引脚以填充间隙,以防止干扰现有的引脚连接。

设置订单的改进:

将对话框更改为无模式,以便在打开对话框时可以查看设计(平移,缩放等)。

添加了一个复选框,用于在操作期间选择使设计变暗。

现在可以在设计中选择对话框中列出的模板,该模板会在对话框中突出显示它们。

在PCB设计中,您现在可以将元件焊盘,安装孔和过孔制作为星形点,以连接到多个网络。星点现在可以命名。

现在,使用“测量”工具时,可以在新的“角度”选项卡上显示所选项目的侧面(例如,“文档形状”,“构造线”,“轨迹”等)之间的角度。将显示一条弯曲的测量线,以显示正在测量的是哪两个侧面。

如果双击斜接,则仅当其小于“编辑轨迹”选项中默认斜接大小的两倍时,才输入“编辑斜接”。

在面板设计中,“在PCB周围创建Tab-Rout”功能现在将遵循面板设计规则,并退出Tab-Rout,以避免Panel Outline,V-Scores,Tab-Routs和其他PCB实例。如果可能,将在后退间隙(凸耳)内添加钻孔(鼠标咬合)。

在面板设计中,如果使用“创建突围选项卡”在弯曲的突舌-弧形线段中插入带有钻孔(鼠标咬合)的突舌,则这些孔将遵循电路板轮廓中曲线的轮廓。

新的文档符号类型“总线参考”。在添加总线形状时,可以使用“插入总线参考”,也可以使用“启动-总线参考”或“结束-总线参考”将这些符号添加到原理图设计中。使用它们连接到总线的末端以显示其网络名称范围。

现在,您可以在添加铜和模板形状的同时将它们分配给网络。可以在开始第一个点之前或添加形状时从上下文菜单中完成此操作。如果您有一个类似的项目被预选,那么将会从中获取净额。如果您预选了其他类型的物品(例如轨道),则将从该物品中取出网罩,并发出警告,询问您是否要使用该网罩。

当您使用“添加轨道”为“差分对”添加成对的轨道线段并且越过另一边具有不同“轨道样式”或“差分对间隙”的区域边界时,当前的配对会自动在边界的近侧停止,并在另一端在边界上添加了两个过渡轨道,将配对部分的末端连接在一起。如果输入区域是错误的,请使用退格键几次以删除“区域”过渡轨迹,然后还原为编辑原始的配对轨迹。

12、报告制作者

现在,您可以在“过孔列表”命令中使用“层列表”,然后使用新的层命令“通过附加到”来报告将当前过孔附加到该层的项目。

现在可以输出匹配对规则的最小和最大间距值。

错误标记的更改:

New Add Error Marker命令可将新的用户定义错误(类型“UDE”)添加到设计中。

新的“删除错误标记”命令可从设计中删除任何错误标记。

现在,在大多数情况下,在错误标记上使用“规则名称”命令将报告错误原因的规则名称。

用于报告库,步骤模型或3D封装的当前路径的新命令,用于PCB或原理图设计中的项目。

用于从保管库浏览器报告“在哪里使用”和“引用到”列表的新命令。

现在,在设计级别可以使用列表命令“保管库项目修订列表”和“保管库项目审核条目列表”。这些可用于将版本历史记录插入设计中。它们也可以用于报告设计中的哪些项目(设计,零件,符号和文档符号)不是Vault中的最新版本。

现在,新命令“库项目版本”和“库中的最新版本”可用于设计,零件,封装,原理图符号,文档符号和相关零件。这些命令可用于检查设计是否具有其零件和符号的最新版本。

变量命令的新功能。现在有一个“转换文本”操作,可让您以指定的方式转换变量值。选项包括“大写”,“小写”,“在开始时删除空白”和“在结尾时删除空白”。

新命令“属性位置列表”用于报告有关设计,页面,组件上每个属性位置的信息。对于每个属性位置,您可以报告其位置,有关其属性的详细信息以及新命令“已显示”,以便仅在设计中显示它们时报告它们。此列表的一个示例用法是报告设计中胶点位置的列表。每个组件都分配了一个“胶点”属性,并在胶点应添加的位置添加了许多属性位置。

新命令“星点列表”用于报告有关设计,页面或网络中每个星点的信息。现在,在PCB设计中需要星点可以位于组件焊盘和过孔上。已安装的“Star Points.rff”脚本已更改为使用此命令。

在起始点,引脚,过孔,安装孔或文档符号列表中使用了新命令“星形点名称”。如果该项目不是星号,则为空白。

引脚,过孔,安装孔或文档符号列表中使用了新命令“是星形点”。

现在,所有“列表项”命令都有一个额外的排序级别。

对于Attribute命令,您现在可以选择使用变量名称定义所需的属性名称。运行报表时,将从命名变量的内容中提取所需的属性名称。

13、工具

倒铜

新的选项可以在垫角附近摆正。

使用模板的中心线作为铜的范围的新选项。

如有必要,Copper Pour现在将插入方头辐条以适合不适合圆头辐条的地方。

设计规则检查

对于大多数错误代码,“设计规则检查”现在将报告作为错误原因的规则。

设计规则检查现在可以重新检查锁定的错误,删除那些现在不是错误的错误。

电气规则检查现在具有“显示错误栏”选项。

新的用户定义错误标记(类型“UDE”),仅通过报表制作工具添加到设计中(请参见上文)。

现在,在检查Tab-Routs和V-Scores时,面板设计还有一些其他的设计级别间距。

同步化

PCB设计中同步设计设置中的新开关“Apply Net Class Changes”。对于某些在PCB中具有网类但在原理图中没有网类的导入格式,需要将其关闭。

为了改善“测试点同步”,现在在原理图设计中创建时,它们用唯一的ID进行了标记,从而可以映射到PCB设计中的匹配测试点。因此,在先前版本中完全同步并包含测试点的任何一对设计现在都将产生差异报告,该报告指出连通性相同,但最好将PCB更新以达到未来的匹配性能。更新会将ID复制到PCB测试点。

14、找

查找栏具有新的查找类别,即“查找跟踪”,“查找连接”和“查找步骤模型”。

15、从库中重新加载

现在,从库中重新加载“保留属性样式和位置”选项分为“保留属性样式”和“保留属性位置”选项。对“更改零件”,“备用零件”和“替换零件”选项进行了相同的更改。

16、图书馆经理

新的“拖放”功能,用于将外来设计和库添加到Pulsonix库。

17、切换图层设置

其他选项已添加到“切换图层”对话框中,以允许您在添加或编辑图层切换时从一系列字段中选择特定属性,而不必手动输入切换图层命令。

18、报告书

添加了新的PCB标准报告“逐层跟踪”。这将报告设计中每个图层上使用的轨道宽度以及轨道样式名称。

新用户报告:

检查库版本-对于设计,报告哪些项目的版本小于库中的最新版本。

检查保管库版本-对于设计,报告哪些项目的版本小于保管库中的最新版本。

保管库项目过时警告-对于设计,请报告哪些项目的版本小于保管库中的最新版本。将过时的每个项目的警告标记添加到设计中。

保管库过期项目-在保管库浏览器中使用,以报告当前浏览器列表中已过期(不是最新版本)的项目所使用的保管库中的所有项目。

保管库引用至-在保管库浏览器中使用,以报告当前浏览器列表中的项目所使用的保管库中的所有项目。例如,报告设计文件使用的所有零件和足迹。

保管箱使用位置-在保管箱浏览器中使用,用于报告保管箱中使用当前浏览器列表中项目的所有位置。例如,您可以使用它来快速查找使用特定足迹的所有零件,或使用特定零件的所有设计。

设计计算器

轨道阻抗计算器可与无模式对话框一起使用,允许光标“探测”每个轨道以进行检查。将鼠标悬停在轨道上将显示一个活动的工具提示弹出窗口,其中显示了轨道阻抗结果。

19、金库

“文件”菜单中提供了新选项“从保管库分离”。从当前设计或库项目中删除保管库信息,因此可以将其作为新项目而不是原始项目的新版本添加回保管库。

现在,除了在检查过程中显示对话框外,还可以从Vault浏览器访问“更新Vault交叉引用”对话框。它可作为“保管库浏览器项目”列表上下文菜单上的“更新对选定项目的引用”选项。

20、数据库连接

现在,“数据库类型”对话框具有一个附加的“高级”按钮,该按钮将显示系统上安装的所有ODBC驱动程序的列表,并允许选择其他选项。

21、导出OrCAD网表

增加了在OrCAD网表中输出中性网和零件名称的功能,以隐藏公司的特定名称,以帮助保护设计IP。

22、导入智能Gerber

现在,您可以使用拖放操作将文件添加到Intelligent Gerber Import对话框中。读入每个文件后,您将看到显示的“文件设置”对话框,您可以在其中选择图层映射。

功能特色

1、原理图捕获

在这种易于使用的设计环境中创建清晰简洁的示意图。无需繁琐的菜单或命令即可通过无模式操作和直观的用户界面进行导航。

多级分层设计:使用预定义的模块,便于重复使用常用的电路元件。

电气规则检查:在设计和进行交互式批处理时,在线进行电气规则检查可确保在创建电路期间始终遵守您的设计规则。

即时交叉探针:在原理图和PCB设计之间进行双向交叉探针,以确保设计的准确性和正确性。

广泛的库:使用组件搜索引擎,并从超过1500万个可用零件中选择您可以使用的组件。将它们直接拖放到您的设计中。

2、集成Spice仿真

Spice仿真

Pulsonix Spice已完全集成到Pulsonix设计环境中,是一种先进的混合模式仿真程序包,其性能优于市场上许多其他Spice工具。

先进的波形分析:全面的分析功能选择可以应用于绘图数据。只需单击鼠标,就可以计算RMS,上升和下降时间,-3dB点或许多其他功能,并在图例旁边显示。

随机探测:Pulsonix Spice包括模拟后的随机探测。成功完成模拟后,就像在实验室中使用示波器一样,探查原理图设计,并在分析图窗口中查看结果。

集成库:使用与原理图和PCB设计相同的库。在此环境中可以使用Spice模型,控制元素和原语。

3、PCB布局

Pulsonix PCB设计环境经过精心设计,可确保以最少的学习时间获得最高的生产率。

规则创建,组件放置,布线模式和后处理功能等多种功能可大幅减少您的设计时间。

导入过滤器:业界最大的导入过滤器,可让您保留外观设计和图书馆的知识产权。

设计变体:满足您设计要求的完整装配体变体。

PCB-3D协同设计环境:将您的PCB布局传递到集成的3D环境中以查看设计和外壳,然后运行冲突检测。进行位置更改以解决冲突,此注释会自动传递回PCB编辑器,所有这些都在Pulsonix内部。

4、高速设计

高速设计

Pulsonix支持一组强大的约束驱动,基于规则的交互式高速设计功能。

原理图驱动规则:从原理图驱动,工程师可以在早期逻辑捕获阶段构思和定义设计。所有约束规则都会自动传递到PCB设计。

约束驱动的设计规则:定义关键的高速设计规则,在布局阶段必须遵守这些规则。

信号路径:信号路径使您可以创建在设计中需要特别考虑的特定路径,这对于DDR,USB和PCI Express设计是必不可少的。

蛇形布线:使用定义的设计规则以交互方式将长度添加到走线中。

5、先进的技术

Pulsonix为您的现代设计要求提供了先进的技术功能。

灵活的刚性设计:通过多跨层区域,电路板轮廓,电路板切口和跨层组件的真正的Flexi-Rigid支持使您轻松实现高级设计要求。

支持埋入式组件:此高级功能集支持跨越电介质层的印刷电阻器和电容器以及跨多层的平面变压器形式的埋入式组件。

支持薄型芯片:还支持真正的先进技术,包括将物理组件和薄型芯片埋入板的层状基板内的空腔中。

板载芯片支持:允许在设计中自动交互地创建和标注管芯和键合焊盘以及键合线。

6、Pulsonix保管箱

保管箱管理员

通过Pulsonix Vault,可以对原理图设计,层次结构块,PCB设计,面板,技术文件和Pulsonix库进行真正的修订和访问控制。

免费:所有Pulsonix SCM/PCB系统均免费提供Pulsonix Vault。

数据控制:以受控方式使用已知和经过验证的数据,以确保准确性并减少操作错误。

全面审核验证:保险柜跟踪并记录所有更改。这意味着您不仅可以对保管库活动进行全面审核,而且还可以查看迭代之间项目的物理更改,并查看谁进行了更改。

灵活的数据库:Vault可以根据您的要求而位于本地或远程,例如它的灵活性。

7、数据库连接

通过Pulsonix数据连接(“PDC”),可以立即访问公司信息系统,以快速识别和选择组件。

灵活:在原理图和PCB设计编辑器中都可以选择零件。

参数化零件选择:数据库界面通过对数据进行参数化搜索来实现真正的零件选择。

零件预览:在将其放入设计之前,请查看并验证您选择的原理图符号或PCB封装。

直接连接:PDC使用标准的ODBC连接,这意味着您可以连接到使用此协议的任何数据存储库,例如MS Access,Excel,MySQL,SAP,Oracle甚至某些文本编辑器!

8、PLM接口

PLM连接

PLM产品界面(PLM系统与各种工具之间的中间层应用程序)允许以受控方式访问文档和其他设计数据。

零件预览:在贵公司使用PLM系统的地方,Pulsonix为基本命令和数据提供了“挂钩”。

流程:所有动作均符合PLM系统定义的设计流程。然后,每个过程也是完整审核跟踪的一部分。

强大的命令驱动:Pulsonix PLM界面中强大的命令集使您可以编写进程。

9、数据迁移

所有SCM/PCB设计产品中最大的进口过滤器阵列。将设计和库从当前系统导入Pulsonix,并保留您的知识产权。

安装激活教程

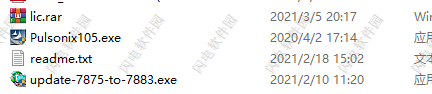

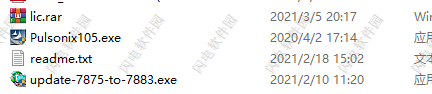

1、在本站下载并解压,如图所示

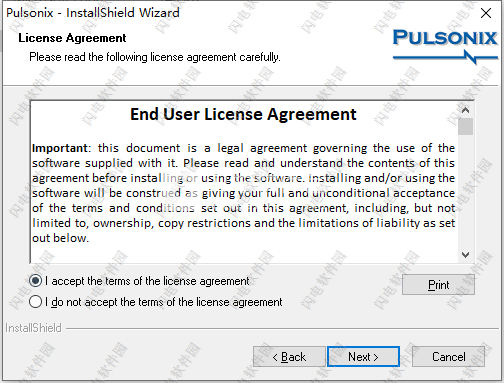

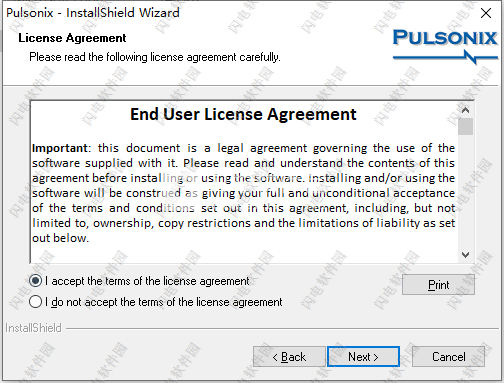

2、双击Pulsonix105.exe运行安装,勾选我接受许可证协议条款

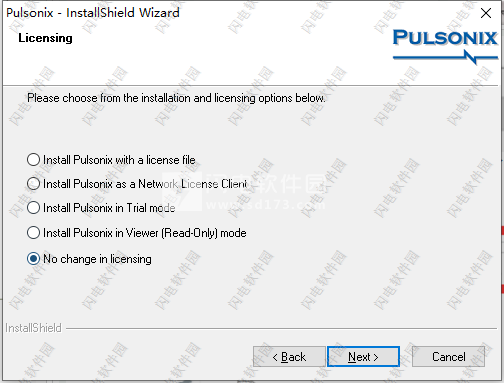

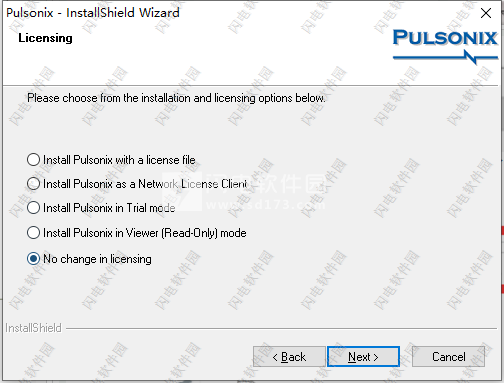

3、勾选最后一项

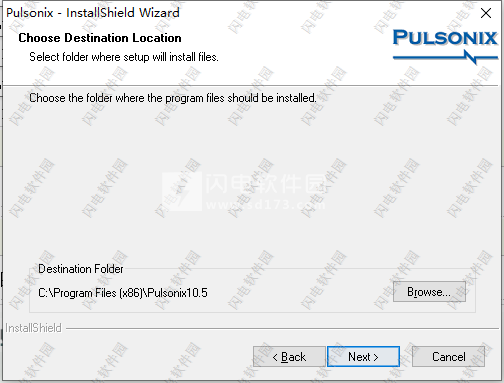

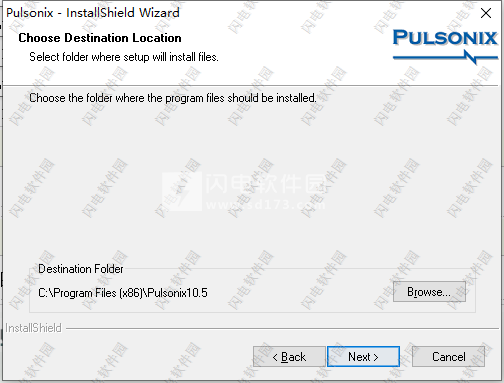

4、点击next,选择软件安装路径

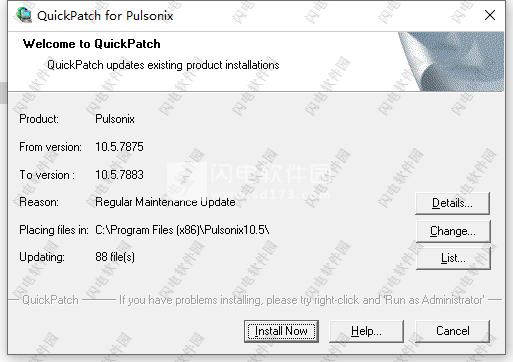

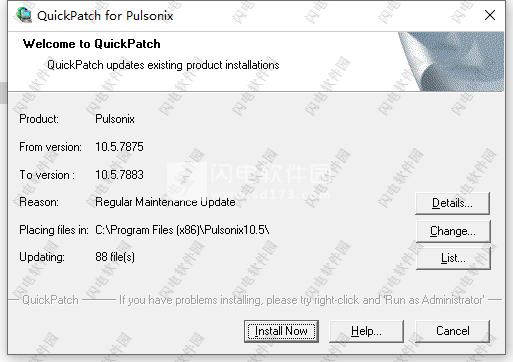

5、安装完成,退出向导,运行update-7875-to-7883.exe,确认安装信息,点击install

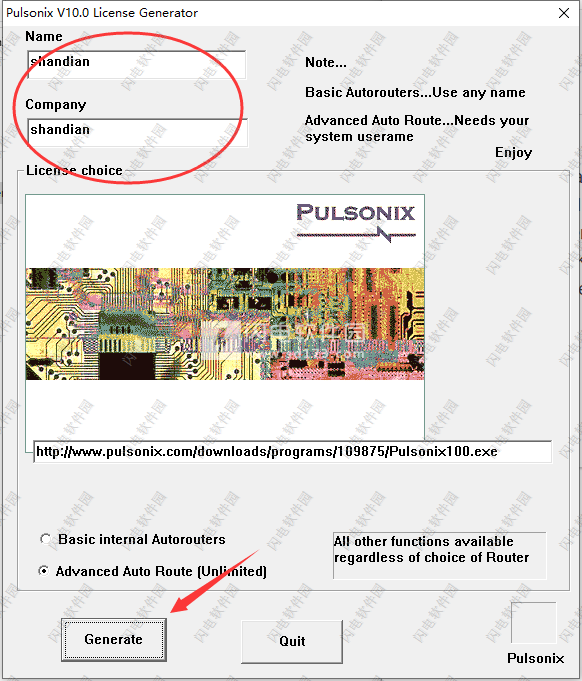

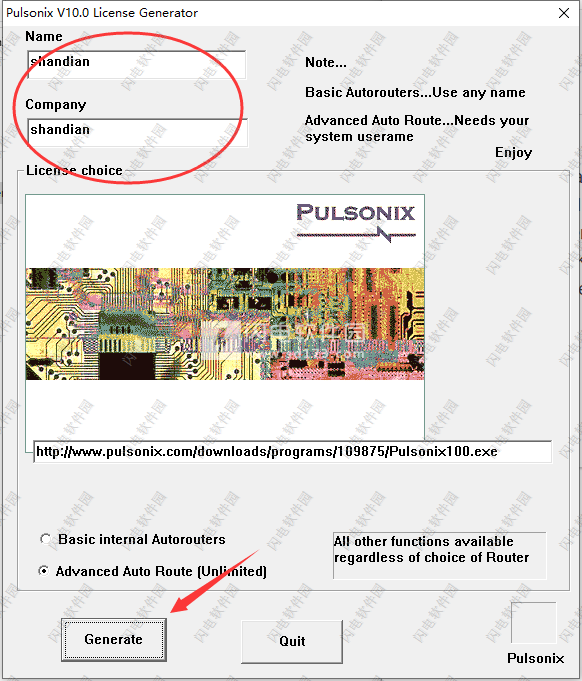

6、将lic文件夹复制到安装目录中,管理员身份运行Pulsonix 10.0 Keygen.exe,点击generate生成按钮,注意生成的许可证的名称必须是Windows的登录名

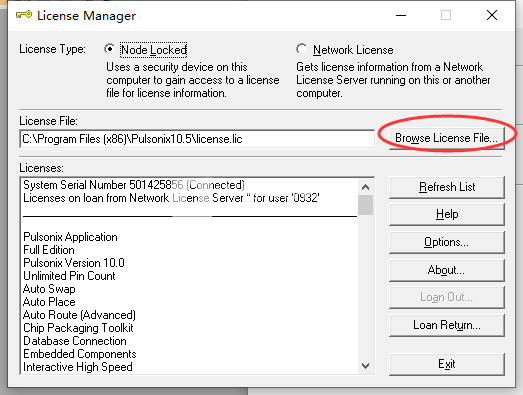

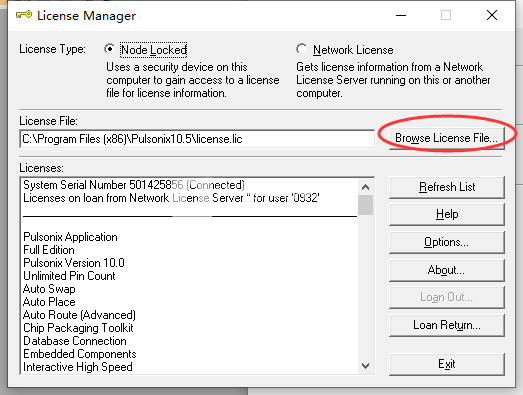

7、运行 License manager,然后选择我们刚才生成的License.lic文件

闪电小编说明:

使用支持进行从简单的单页电路到复杂的真实实例层次设计。功能强大的电路板布局工具,采用最新的制造技术。完全集成到PCB布局中,易于使用。看从其他Schematic / CAE系统导入设计和库,从其他Schematic / CAE系统导入网表,基于功能强大的向导的Cadence Specctra界面,以及指向Zuken Route Editor的链接。许多内置CAM输出和功能强大的Report Maker,可生成您自己的数据文件格式。

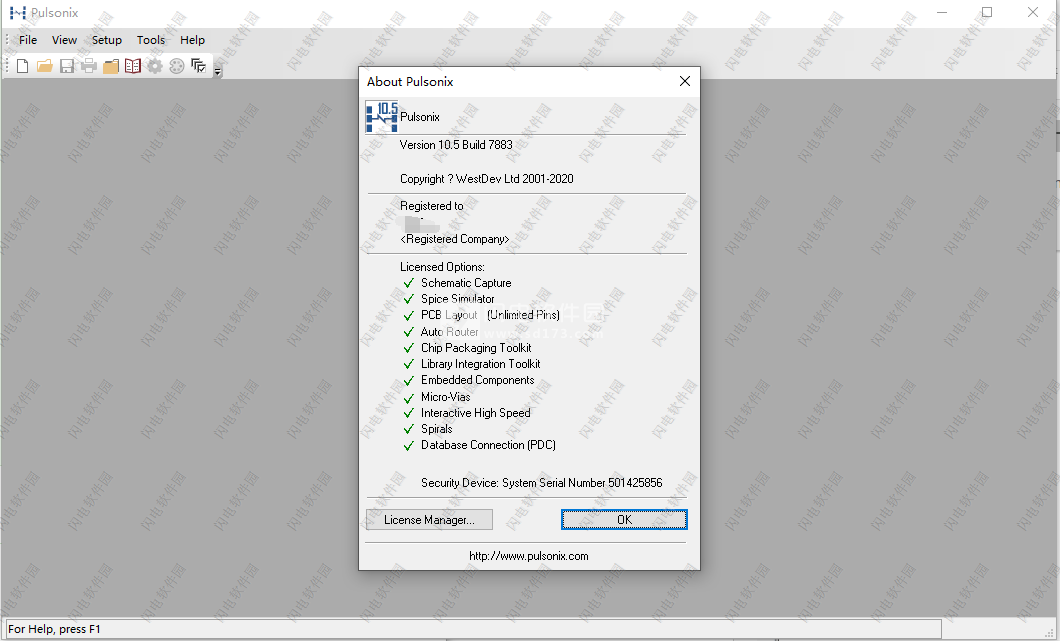

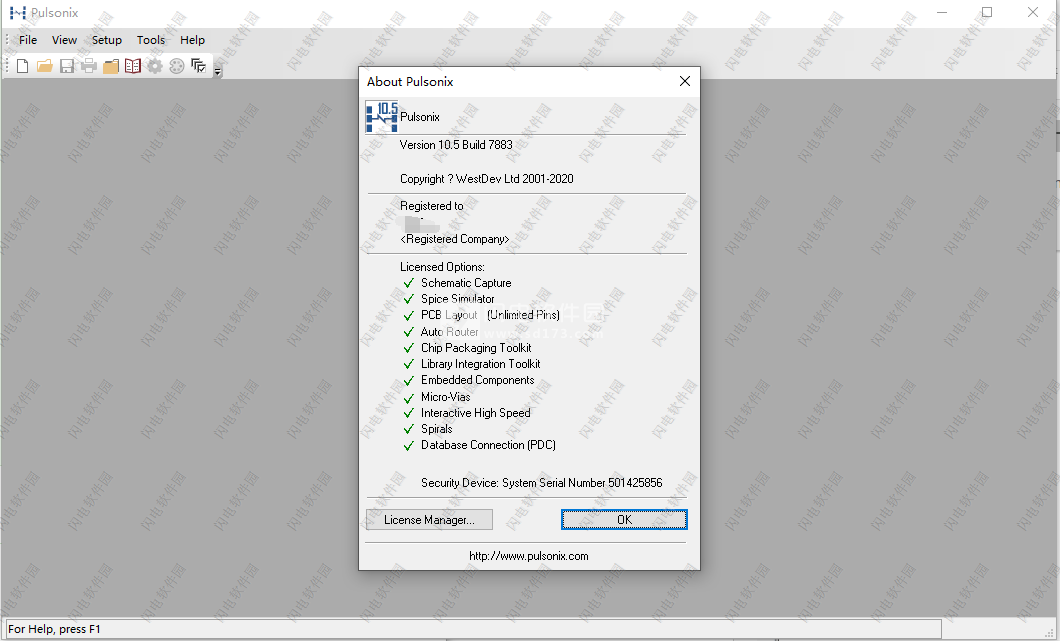

Pulsonix 10.5 build 7883 许可证授权激活教程

Pulsonix 10.5 build 7883 许可证授权激活教程

Pulsonix 10.5 build 7883 许可证授权激活教程

Pulsonix 10.5 build 7883 许可证授权激活教程